Fifth International Workshop on Formal Techniques for Safety-Critical Systems (FTSCS 2016)

Preliminary Proceedings

Editors: Cyrille Artho and Peter Csaba Ölveczky

## Preface

This volume contains the preliminary proceedings of the *Fifth International Workshop on Formal Techniques for Safety-Critical Systems* (FTSCS 2016), held in Tokyo November 14, 2016, as a satellite event of the ICFEM conference.

The aim of this workshop is to bring together researchers and engineers who are interested in the application of formal and semi-formal methods to improve the quality of safety-critical computer systems. FTSCS strives to promote research and development of formal methods and tools for industrial applications, and is particularly interested in industrial applications of formal methods. Specific topics include, but are not limited to:

- case studies and experience reports on the use of formal methods for analyzing safety-critical systems, including avionics, automotive, railway, medical, and other kinds of safety-critical and QoS-critical systems;

- methods, techniques and tools to support automated analysis, certification, debugging, etc., of complex safety/QoS-critical systems;

- analysis methods that address the limitations of formal methods in industry (usability, scalability, etc.);

- formal analysis support for modeling languages used in industry, such as AADL, Ptolemy, SysML, SCADE, Modelica, etc.; and

- code generation from validated models.

The workshop received 23 regular paper submissions. Each submission was reviewed by at least three referees. Based on the reviews and extensive discussions, the program committee selected 9 papers for presentation at the workshop and inclusion in this volume. Another highlight of the workshop is an invited talk by Naoki Kobayashi.

Revised versions of accepted papers will appear in the post-proceedings of FTSCS 2016 that will be published as a volume in Springer's *Communications in Computer and Information Science* (CCIS) series. Extended versions of selected papers from the workshop will also appear in a special issue of the *Science of Computer Programming* journal.

Many colleagues and friends have contributed to FTSCS 2016. We thank Naoki Kobayashi for accepting our invitation to give an invited talk and the authors who submitted their work to FTSCS 2016 and who, through their contributions, make this workshop an interesting event. We are particularly grateful that so many well known researchers agreed to serve on the program committee, and that they provided timely, insightful, and detailed reviews. We also thank the editors of *Communications in Computer and Information Science* for agreeing to publish the proceedings of FTSCS 2016 as a volume in their series, and Shaoying Liu and Shin Nakajima for their help with the local arrangements.

We hope that you will all enjoy the workshop!

November, 2016

Cyrille Artho Peter Csaba Ölveczky

# **Program Chairs**

| Cyrille Artho        | KTH Royal Institute of Technology |

|----------------------|-----------------------------------|

| Peter Csaba Ölveczky | University of Oslo                |

# Program Committee

| Étienne André        | University Paris 13                             |

|----------------------|-------------------------------------------------|

| Toshiaki Aoki        | JAIST                                           |

| Cyrille Artho        | KTH Royal Institute of Technology               |

| Kyungmin Bae         | Pohang University of Science and Technology     |

| Eun-Hye Choi         | AIST                                            |

| Alessandro Fantechi  | University of Florence and ISTI-CNR, Pisa       |

| Bernd Fischer        | Stellenbosch University                         |

| Osman Hasan          | National University of Sciences & Technology    |

| Klaus Havelund       | NASA JPL                                        |

| Jérôme Hugues        | Institute for Space and Aeronautics Engineering |

| Marieke Huisman      | University of Twente                            |

| Ralf Huuck           | Synopsys                                        |

| Fuyuki Ishikawa      | National Institute of Informatics               |

| Takashi Kitamura     | AIST                                            |

| Alexander Knapp      | Augsburg University                             |

| Thierry Lecomte      | ClearSy System Engineering                      |

| Yang Liu             | Nanyang Technological University                |

| Robi Malik           | University of Waikato                           |

| Frédéric Mallet      | Université Nice Sophia Antipolis                |

| Roberto Nardone      | University of Napoli "Federico II"              |

| Vivek Nigam          | Federal University of Paraíba                   |

| Thomas Noll          | RWTH Aachen University                          |

| Kazuhiro Ogata       | JAIST                                           |

| Peter Csaba Ölveczky | University of Oslo                              |

| Charles Pecheur      | Université catholique de Louvain                |

| Markus Roggenbach    | Swansea University                              |

| Ralf Sasse           | ETH Zürich                                      |

| Martina Seidl        | Johannes Kepler University Linz                 |

| Oleg Sokolsky        | University of Pennsylvania                      |

| Sofiène Tahar        | Concordia University                            |

| Carolyn Talcott      | SRI International                               |

| Tatsuhiro Tsuchiya   | Osaka University                                |

| András Vörös         | Budapest University of Technology and Economics |

| Chen-Wei Wang        | State University of New York (SUNY)             |

| Mike Whalen          | University of Minnesota                         |

| Huibiao Zhu          | East China Normal University                    |

|                      |                                                 |

## **Additional Reviewers**

Beillahi, Sidi Mohamed Bukhari, Syed Ali Asadullah Du, Xiaoning Fang, Huixing Gentile, Ugo Gillard, Xavier Oortwijn, Wytse Qasim, Muhammad Sardar, Muhammad Usama Van Zijl, Lynette

## Table of Contents

## Invited Talk

| On Two | Higher-Order | Extensions | of Model | Checking. | <br> | 1 |

|--------|--------------|------------|----------|-----------|------|---|

| Naoki  | Kobayashi    |            |          |           |      |   |

## Specification and Verification

| Specification and Verification of Synchronization with Condition Variables | 3  |

|----------------------------------------------------------------------------|----|

| Pedro de Carvalho Gomes, Dilian Gurov and Marieke Huisman                  |    |

| An interval logic for stream-processing functions: A convolution-based     |    |

| construction                                                               | 19 |

| Brijesh Dongol                                                             |    |

## Automotive and Railway Systems

| Automating Time Series Safety Analysis for Automotive Control                |    |

|------------------------------------------------------------------------------|----|

| Systems in STPA using Weighted Partial Max-SMT                               | 35 |

| Shuichi Sato, Shogo Hattori, Hiroyuki Seki, Yutaka Inamori and Shoji<br>Yuen |    |

| Uniform Modeling of Railway Operations<br>Eduard Kamburjan and Reiner Hähnle | 51 |

## Security, Internet of things

| Formal Verification of Gate-Level Multiple Side Channel Parameters to |    |

|-----------------------------------------------------------------------|----|

| detect Hardware Trojans                                               | 68 |

| Imran Abbasi, Faiq Khalid Lodhi, Awais Kamboh and Osman Hasan         |    |

| Formal Probabilistic Analysis of a WSN-based Monitoring Framework     |    |

| for IoT Applications                                                  | 85 |

| Maissa Elleuch, Osman Hasan, Sofiène Tahar and Mohamed Abid           |    |

## Cyber-Physical Systems and Parameterized Verification

| Shared-Variable Concurrency, Continuous Behaviour and Healthiness for  |

|------------------------------------------------------------------------|

| Critical Cyberphysical Systems 101                                     |

| Richard Banach and Huibiao Zhu                                         |

| Applying parametric model-checking techniques for reusing real-time    |

| critical systems                                                       |

| Baptiste Parquier, Laurent Rioux, Rafik Henia, Romain Soulat,          |

| Olivier H. Roux, Didier Lime and Étienne André                         |

| Parameterised Verification of Stabilisation Properties via Conditional |

| Spotlight Abstraction                                                  |

| Nils Timm and Stefan Gruner                                            |

## On Two Higher-Order Extensions of Model Checking

Naoki Kobayashi

The University of Tokyo koba@is.s.u-tokyo.ac.jp

Inspired by the success of finite state model checking [1] in system verification, two kinds of its higher-order extensions have been studied since around 2000. One is model checking of higher-order recursion schemes (HORS) [2, 10], where the language for describing systems to be verified is extended to higher-order, and the other is higher-order fixpoint modal logic (HFL) model checking of finite-state systems [14], where the logic for specifying properties to be verified is extended to higher-order. The former has been successfully applied to automated verification of higher-order programs [3, 4, 6–8, 11–13, 15], whereas the latter has been studied for verification of concurrent systems [9, 14]. In the talk, I will provide a gentle introduction to the HORS and HFL model checking problems, their applications to software verification, and the state-of-the-art of higher-order model checkers and tools built on top of them. I will also touch upon our recent result on the relationship between HORS and HFL model checking [5].

## References

- 1. Clarke, E.M., Grumberg, O., Peled, D.A.: Model Checking. The MIT Press (1999)

- Knapik, T., Niwinski, D., Urzyczyn, P.: Higher-order pushdown trees are easy. In: FoSSaCS 2002. LNCS, vol. 2303, pp. 205–222. Springer (2002)

- Kobayashi, N.: Types and higher-order recursion schemes for verification of higherorder programs. In: Proc. of POPL. pp. 416–428. ACM Press (2009)

- Kobayashi, N.: Model checking higher-order programs. Journal of the ACM 60(3) (2013)

- Kobayashi, N., Étienne Lozes, Bruse, F.: On the relationship between higher-order recursion schemes and higher-order modal fixpoint logic. In: Proceedings of POPL 2017 (2017), to appear

- Kobayashi, N., Sato, R., Unno, H.: Predicate abstraction and CEGAR for higherorder model checking. In: Proc. of PLDI. pp. 222–233. ACM Press (2011)

- Kobayashi, N., Tabuchi, N., Unno, H.: Higher-order multi-parameter tree transducers and recursion schemes for program verification. In: Proc. of POPL. pp. 495–508. ACM Press (2010)

- Kuwahara, T., Sato, R., Unno, H., Kobayashi, N.: Predicate abstraction and CE-GAR for disproving termination of higher-order functional programs. In: Proceedings of CAV 2015. Lecture Notes in Computer Science, vol. 9207, pp. 287–303. Springer (2015)

- Lange, M., Lozes, É., Guzmán, M.V.: Model-checking process equivalences. Theor. Comput. Sci. 560, 326–347 (2014)

- Ong, C.H.L.: On model-checking trees generated by higher-order recursion schemes. In: LICS 2006. pp. 81–90. IEEE Computer Society Press (2006)

- 11. Ong, C.H.L., Ramsay, S.: Verifying higher-order programs with pattern-matching algebraic data types. In: Proc. of POPL. pp. 587–598. ACM Press (2011)

- Sato, R., Unno, H., Kobayashi, N.: Towards a scalable software model checker for higher-order programs. In: Proceedings of PEPM 2013. pp. 53–62. ACM Press (2013)

- Unno, H., Terauchi, T., Kobayashi, N.: Automating relatively complete verification of higher-order functional programs. In: The 40th Annual ACM SIGPLAN-SIGACT Symposium on Principles of Programming Languages, POPL 2013. pp. 75–86. ACM (2013)

- 14. Viswanathan, M., Viswanathan, R.: A higher order modal fixed point logic. In: CONCUR. Lecture Notes in Computer Science, vol. 3170, pp. 512–528 (2004)

- Watanabe, K., Sato, R., Tsukada, T., Kobayashi, N.: Automatically disproving fair termination of higher-order functional programs. In: Proceedings of ICFP 2016. pp. 243–255. ACM (2016)

## Specification and Verification of Synchronization with Condition Variables

Pedro de Carvalho Gomes<sup>1</sup>, Dilian Gurov<sup>1</sup>, and Marieke Huisman<sup>\*2</sup>

KTH Royal Institute of Technology, Stockholm, Sweden

<sup>2</sup> University of Twente, Enschede, The Netherlands

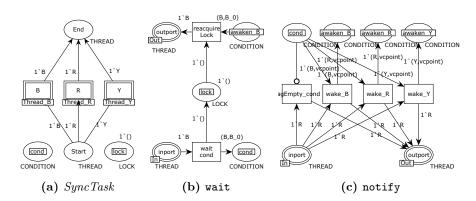

In this paper we propose a technique to specify and verify the correct synchro*nization* of concurrent programs with condition variables. We define correctness as the liveness property: "every thread synchronizing under a set of condition variables eventually exits the synchronization", under the assumption that every such thread eventually reaches its synchronization block. Our technique does not avoid the combinatorial explosion of interleavings of thread behaviors. Instead, we alleviate it by abstracting away all details that are irrelevant to the synchronization behavior of the program, which is typically significantly smaller than its overall behavior. First, we introduce SyncTask, a simple imperative language to specify parallel computations that synchronize via condition variables. We consider a SyncTask program to have a correct synchronization iff it terminates. Further, to relieve the programmer from the burden of providing specifications in SyncTask, we introduce an economic annotation scheme for Java programs to assist the *automated extraction* of SyncTask programs capturing the synchronization behavior of the underlying program. We prove that every Java program annotated according to the scheme (and satisfying the assumption) has a correct synchronization iff its corresponding SyncTask program terminates. We show how to transform the verification of termination into a standard reachability problem over Colored Petri Nets that is efficiently solvable by existing Petri Net analysis tools. Both the SyncTask program extraction and the generation of Petri Nets are implemented in our STAVE tool. We evaluate the proposed framework on a number of test cases as a proof-of-concept.

## 1 Introduction

*Condition variables* (CV) are a commonly used synchronization mechanism to coordinate multithreaded programs. Threads *wait* on a CV, meaning they suspend their execution until another thread *notifies* the CV, causing the waiting threads to resume their execution. The signaling is asynchronous: if no thread is waiting on the CV, then the notification has no effect. CVs are used in conjunction with locks; a thread must acquire the associated lock for notifying or waiting on a CV, and if notified, must reacquire the lock.

Many widely used programming languages feature condition variables. In Java, for instance, they are provided both natively as an object's *monitor* [6], i.e., a pair of a lock and a CV, and in the concurrent API, as one-to-many

<sup>\*</sup> Supported by ERC grant 258405 for the VerCors project.

### 2 Pedro de Carvalho Gomes, Dilian Gurov, and Marieke Huisman

Condition objects associated to a Lock object. The mechanism is typically employed when the progress of threads depends on the state of a shared variable, to avoid busy-wait loops that poll the state of this shared variable. Nevertheless, condition variables have not been addressed sufficiently with formal techniques, mainly because of the complexity of reasoning about asynchronous signaling. For instance, Leino *et al.* [14] acknowledge that verifying the absence of deadlocks when using CVs is hard because a notification is "lost" if no thread is waiting on it. Thus, one cannot verify locally whether a waiting thread will eventually be notified. Furthermore, the synchronization conditions can be quite complex, involving both control-flow and data-flow aspects as arising from method calls; their correctness thus depends on the *global thread composition*, i.e., the type and number of parallel threads. All these complexities suggest the need for *programmer-provided annotations* to assist the automated analysis, which is the approach we are following here.

In this work, we present a formal technique for specifying and verifying that "every thread synchronizing under a set of condition variables eventually exits the synchronization", under the assumption that every such thread eventually reaches its synchronization block. The assumption itself is not addressed here, as it does not pertain to correctness of the synchronization, and there already exist techniques for dealing with such properties (see e.g. [16]). Note that the above correctness notion applies to a *one-time synchronization* on a condition variable only; generalizing the notion to repeated synchronizations is left for future work. To the best of our knowledge, the present work is the first to address a *liveness* property involving CVs. As the verification of such properties is undecidable in general, we limit our technique to programs with bounded data domains and numbers of threads. Still, the verification problem is subject to a combinatorial explosion of thread interleavings. Our technique alleviates the state space explosion problem by *delimiting the relevant aspects of the synchronization*.

First, we consider correctness of synchronization in the context of a synchronization specification language. As we target arbitrary programming languages that feature locks and condition variables, we do not base our approach on a subset of an existing language, but instead introduce SyncTask, a simple concurrent programming language where all computations occur inside synchronized code blocks. We define a SyncTask program to have a correct synchronization iff it terminates. The SyncTask language has been designed to capture common patterns of CV usage, while abstracting away from irrelevant details. SyncTask has a Java-like syntax and semantics, and features the relevant constructs for synchronization, such as locks, CVs, conditional statements, and arithmetic operations. However, it is non-procedural, data types are bounded, and it does not allow dynamic thread creation. These restrictions render the state-space of SyncTask programs finite, and make the termination problem decidable.

Next, we address the problem of verifying the correct usage of CVs in real concurrent programming languages by showing how SyncTask can be used to capture the synchronization of a Java program, provided it is bounded. There is a consensus in Software Engineering that synchronization in a concurrent program

3

must be kept to a minimum, both in the number and complexity of the synchronization actions, and in the number of places where it occurs. This avoids the latency of blocking threads, and minimizes the risk of errors, such as dead- and livelocks. As a consequence, many programs present a finite (though arbitrarily large) synchronization behavior. To assist the automated extraction of finite synchronization behavior from Java programs as SyncTask programs, we introduce an *annotation scheme*, which requires the user to (correctly) annotate, among others, the initialization of new threads (i.e., creation of **Thread** objects), and provide the initial state of the variables accessed inside the synchronized blocks. We establish that for correctly annotated, bounded Java programs, correctness of synchronization is equivalent to termination of the extracted SyncTask program.

As a proof-of-concept of the algorithmic solvability of the termination problem for SyncTask programs, we show how to transform it into a reachability problem on hierarchical Colored Petri Nets<sup>3</sup> (CPNs) [7]. We define how to extract CPNs automatically from SyncTask programs, following a previous technique from Westergaard [18]. Then, we establish that a SyncTask program terminates *if and only if* the extracted CPN always reaches dead markings (i.e., CPN configurations without successors) where the tokens representing the threads are in a unique *end place*. Standard CPN analysis tools can efficiently compute the reachability graphs, and check whether the termination condition holds. Also, in case that the condition does not hold, an inspection of the reachability graph easily provides the cause of non-termination.

We implement the extraction of SyncTask programs from annotated Java and the translation of SyncTasks to CPNs as the STAVE tool. We evaluate the tool on two test-cases, by generating CPNs from annotated Java programs and analyzing these with CPN Tools [8]. The first test-case evaluates the scalability of the tool w.r.t. the size of program code that does not affect the synchronization behavior of the program. The second test-case evaluates the scalability of the tool w.r.t. the number of synchronizing threads. The results show the expected exponential blow-up of the state-space, but we were still able to analyze the synchronization of several dozens of threads.

In summary, this work makes the following contributions: (i) the SyncTask language to model the synchronization behavior of programs with CVs, (ii) an annotation scheme to aid the extraction of the synchronization behavior of Java programs, (iii) an extraction scheme of SyncTask models from annotated Java programs, (iv) a reduction of the termination problem for SyncTask programs to a reachability problem on CPNs, (v) an implementation of the framework by means of STAVE, and (vi) its experimental evaluation.

The remainder of the paper is organized as follows. Section 2 introduces SyncTask. Section 3 describes the mapping from annotated Java to SyncTask,

<sup>&</sup>lt;sup>3</sup> The choice of formalism has been mainly based on the *simplicity* of CPNs as a general model of concurrency, rather than on the existing support for efficient model checking. For the latter, model checking tools exploiting parametricity or symmetries in the models may prove more efficient in practice.

Pedro de Carvalho Gomes, Dilian Gurov, and Marieke Huisman

| SyncTask ::= ThreadType* Main                                                       | $Block ::= \{ Stmt^* \}$        |

|-------------------------------------------------------------------------------------|---------------------------------|

| $ThreadType ::= Thread ThreadName { SyncBlock* }$                                   | Assign ::= VarName = Expr;      |

| <pre>Main ::= main { VarDecl* StartThread* }</pre>                                  | $Stmt ::= SyncBlock \mid Block$ |

| StartThread ::= start(Const, ThreadName);                                           | Assign  skip;                   |

| $Expr ::= Const \mid VarName \mid Expr \oplus Expr$                                 | while Expr Stmt                 |

| min(VarName)   max(VarName)                                                         | if Expr Stmt else Stmt          |

| VarDecl ::= VarType VarName(Expr*);                                                 | <pre>notify(VarName);</pre>     |

| $VarType ::= \texttt{Bool} \mid \texttt{Int} \mid \texttt{Lock} \mid \texttt{Cond}$ | <pre>notifyAll(VarName);</pre>  |

| SyncBlock ::= synchronized ( $VarName$ ) $Block$                                    | wait(VarName);                  |

| SyncBlock ::= synchronized (VarName) $Block$                                        | wait(VarName);                  |

Fig. 1: SyncTask Syntax

while Section 4 presents the translation into CPNs, and presents test-cases. We discuss related work in Section 5. Section 6 concludes and suggests future work.

## 2 SyncTask

4

SyncTask abstracts from most features of full-fledged programming languages. For instance, it does not have objects, procedures, exceptions, etc. However, it features the relevant aspects of thread synchronization. We now describe the language syntax, types, and semantics.

### 2.1 Syntax and Types

The SyncTask syntax is presented in Figure 1. A program has two main parts:  $ThreadType^*$ , which declares the different types of parallel execution flows, and *Main*, which contains the variable declarations and initializations and defines how the threads are composed, i.e., it statically declares how many threads of each type are spawned.

Each *ThreadType* consists of adjacent *SyncBlocks*, which are mutually exclusive code blocks, guarded by a lock. A code block is defined as a sequence of statements, which may even be another *SyncBlock*. Notice that this allows nested *SyncBlocks*, thus enabling the definition of complex synchronization schemes with more than one lock.

There are four primitive types: booleans (Bool), bounded integers (Int), reentrant locks (Lock), and condition variables (Cond). Expressions are evaluated as in Java. The boolean and integer operators are the standard ones, while max and min return a variable's bounds. Operations between integers with different bounds (overloading) are allowed. However, an out-of-bounds assignment leads the program to an error configuration.

Condition variables are manipulated by the unary operators wait, notify, and notifyAll. Currently, the language provides only two control flow constructs: while and if-else. These suffice for the illustration of our technique, while the addition of other constructs is straightforward.

#### Specification and Verification of Synchronization with CVs

| <pre>1 Thread Producer {     synchronized(m_lock){</pre>                    | <pre>11 Thread Consumer {     synchronized(m_lock){</pre>   | <pre>21 main {    Lock m_lock();</pre>                   |

|-----------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------|

| <pre>3 while(b_els==max(b_els)) wait(m_cond);</pre>                         | <pre>13 while((b_els==0))     wait(m_cond);</pre>           | <pre>23 Cond m_cond(m_lock);<br/>Int b_els(0,1,1);</pre> |

| <pre>5 if(b_els<max(b_els)) b_els="(b_els+1);&lt;/pre"></max(b_els))></pre> | <pre>15 if((b_els&gt;0))             b_els=(b_els-1);</pre> | <pre>25 start(1,Producer);<br/>start(2,Consumer);</pre>  |

| 7 else<br>skip;                                                             | 17 else<br>skip;                                            | 27 }                                                     |

| <pre>9 notifyAll(m_cond); } }</pre>                                         | <pre>19 notifyAll(m_cond); } }</pre>                        |                                                          |

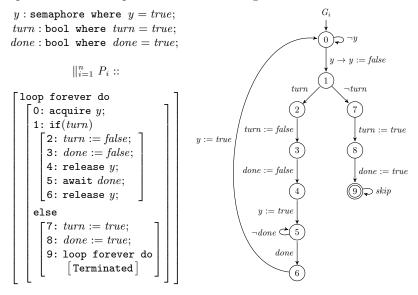

Fig. 2: Modelling of synchronization via a shared buffer in SyncTask

The Main block contains the global variable declarations with initializations (VarDecl\*), and the thread composition (StartThread\*). A variable is defined by its type and name, followed by the initialization arguments. The number of parameters varies per type: Lock takes no arguments; Cond is initialized with a lock variable: Bool takes either a true or a false literal; Int takes three integer literals as arguments: the lower and upper bounds, and the initial value, which must be in the given range. Finally, **start** takes a positive number and a thread type, signifying the number of threads of that type it spawns.

Example 1 (SyncTask program). The program in Figure 2 models synchronization via a shared buffer. Producer and Consumer represent the synchronization behavior: threads synchronize via the CV m\_cond to add or remove elements, and wait if the buffer is full or empty, respectively. Waiting threads are woken up by notifyAll after an operation is performed on the buffer, and compete for the monitor to resume execution. The main block contains variable declarations and initialization. The lock m\_lock is associated to m\_cond. b\_els is an integer in the interval [0,1] (initially set to 1), and represents the number of elements in the buffer. One Producer and two Consumer threads are spawned with start.

#### **Structural Operational Semantics** 2.2

We now define the semantics of SyncTask, to provide the means for establishing formal correctness results.

The semantic domains are defined as follows. Booleans are represented as usual. Integer variables are triples  $\mathbb{Z} \times \mathbb{Z} \times \mathbb{Z}$ , where the first two elements are the lower and upper bound, and the third is the current value. A lock o is a pair (*Thread*  $id \cup \{\bot\}$ ) × N of the id of the thread holding the lock (or  $\bot$ , if none), and a counter of how many times it was acquired. A condition variable d simply stores its respective lock, which is retrieved with the auxiliary function lock(d).

SyncTask contains global variables only and all memory operations are synchronized. Thus, we assume the memory to be sequentially consistent [11]. Let  $\mu$  represent a program's memory. We write  $\mu(l)$  to denote the value of variable l, and  $\mu[l \mapsto v]$  to denote the update of l in  $\mu$  with value v.

A thread state is either running (R) if the thread is executing, waiting (W)if it has suspended the execution on a CV, or *notified* (N) if another thread has woken up the suspended thread. The states W and N also contain the CV d

5

| $[s1]^a$            | $T (\theta, \texttt{synchronized}(o) \ b, R), \mu \longrightarrow T (\theta, \texttt{synchronized}'(o) \ b, R), \mu[o \mapsto (\theta, 1)]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $[s2]^b$            | $T (\theta, \texttt{synchronized}(o) \ b, R), \mu \longrightarrow T (\theta, \texttt{synchronized'}(o) \ b, R), \mu[o \mapsto (\theta, n+1)]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $[s3]^b$            | $\frac{T (\theta, b_1, R), \mu \longrightarrow T (\theta, b_2, X), \mu'}{T (\theta, \text{synchronized}'(o) \ b_1, R)), \mu \longrightarrow T (\theta, \text{synchronized}'(o) \ b_2, X), \mu'}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $[s4]^c$            | $T (\theta, b, R), \mu \longrightarrow T (\theta, \epsilon, R), \mu'$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                     | $T (\theta, \texttt{synchronized'}(o) \ b, R)), \mu \longrightarrow T (\theta, \epsilon, R), \mu'[o \mapsto (\theta, n-1)]$ $T (\theta, b, R), \mu \longrightarrow T (\theta, \epsilon, R), \mu'$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $[s5]^d$            | $\frac{T (\theta, \theta, R), \mu \longrightarrow T (\theta, \epsilon, R), \mu}{T (\theta, \text{synchronized}'(o) \ b, R), \mu \longrightarrow T (\theta, \epsilon, R), \mu'[o \mapsto (\bot, 0)]}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $[wt]^e$            | $T (\theta,\texttt{wait}(d),R),\mu \to T (\theta,\epsilon,(W,d,n)),\mu[\mathit{lock}(d) \mapsto (\bot,0)]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| $[nf1]^{ef}$        | $T (\theta,\texttt{notify}(d),R),\mu \to T (\theta,\epsilon,R),\mu$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $[nf2]^{eg}$        | $T (\theta, \texttt{notify}(d), R) (\theta', t', (W, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, \epsilon, R) (\theta', t', (N, d, n)), \mu \to T (\theta, t', R) (\theta', t', (N, d, n)), \mu \to T (\theta, t', R) (\theta', t', (N, d, n)), \mu \to T (\theta, t', R) (\theta', t', (N, d, n)), \mu \to T (\theta, t', R) (\theta', R) (\theta', t', R) (\theta', R)$ |

| $[na1]^{ef}$        | $T (\theta,\texttt{notifyAll}(d),R),\mu \to T (\theta,\epsilon,R),\mu$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| [na2] <sup>eg</sup> | $T (\theta, \texttt{notifyAll}(d), R) T^d_W, \mu \to T (\theta, \epsilon, R) \{(\theta', t', (N, d, n)) (\theta', t', (W, d, n)) \in T^d_W\}, \mu \in T^d_W\}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $[rd]^h$            | $T (\theta,t,(N,d,n)),\mu \rightarrow T (\theta,t,R),\mu[lock(d) \mapsto (\theta,n)]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $a \mu(o) =$        | $(\perp, 0)  {}^{b}\mu(o) = (\theta, n) \land n > 0  {}^{c}\mu(o) = (\theta, n) \land n > 1  {}^{d}\mu(o) = (\theta, 1)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |