# Fourth International Workshop on Formal Techniques for Safety-Critical Systems (FTSCS 2015)

Preliminary Proceedings

Editors: Cyrille Artho and Peter Csaba Ölveczky

### **Preface**

This volume contains the preliminary proceedings of the Fourth International Workshop on Formal Techniques for Safety-Critical Systems (FTSCS 2015), held in beautiful Paris on November 6–7, 2015, as a satellite event of the ICFEM conference.

The aim of this workshop is to bring together researchers and engineers who are interested in the application of formal and semi-formal methods to improve the quality of safety-critical computer systems. FTSCS strives to promote research and development of formal methods and tools for industrial applications, and is particularly interested in industrial applications of formal methods. Specific topics include, but are not limited to:

- case studies and experience reports on the use of formal methods for analyzing safety-critical systems, including avionics, automotive, medical, and other kinds of safety-critical and QoS-critical systems;

- methods, techniques and tools to support automated analysis, certification, debugging, etc., of complex safety/QoS-critical systems;

- analysis methods that address the limitations of formal methods in industry (usability, scalability, etc.);

- formal analysis support for modeling languages used in industry, such as AADL, Ptolemy, SysML, SCADE, Modelica, etc.; and

- code generation from validated models.

The workshop received 46 submissions; 41 of these were regular papers (including 5 tool papers) and 5 were work-in-progress/position papers. Each submission was reviewed by at least three referees. Based on the reviews and extensive discussions, the program committee selected 15 regular papers and two work-in-progress papers for presentation at the workshop and inclusion in this volume. Another highlight of the workshop is an invited talk by José Meseguer.

Revised versions of accepted regular papers will appear in the post-proceedings of FTSCS 2015 that will be published as a volume in Springer's *Communications in Computer and Information Science* (CCIS) series. Extended versions of selected papers from the workshop will also appear in a special issue of the *Science of Computer Programming* journal.

Many colleagues and friends have contributed to FTSCS 2015. First, we would like to thank Kokichi Futatsugi and Hitoshi Ohsaki for initiating this series of workshops. We thank José Meseguer for accepting our invitation to give an invited talk and the authors who submitted their work to FTSCS 2015 and who, through their contributions, make this workshop an interesting event. We are particularly grateful that so many well known researchers agreed to serve on the program committee, and that they all provided timely, insightful, and detailed reviews.

We thank the editors of Communications in Computer and Information Science for agreeing to publish the proceedings of FTSCS 2015 as a volume in their series, and Jan A. Bergstra and Bas van Vlijmen for accepting our proposal to devote a special issue of the Science of Computer Programming journal to extended versions of selected papers from FTSCS 2015. Finally, Étienne André

and Fatiha Zaïdi have been very helpful with the local arrangements, and we thank Andrei Voronkov for the excellent EasyChair conference system.

We hope that you will all enjoy the workshop!

November, 2015

Cyrille Artho Peter Csaba Ölveczky

# Workshop Chair

Hitoshi Ohsaki AIST

## **Program Chairs**

Cyrille Artho AIST

Peter Csaba Ölveczky University of Oslo

## Program Committee

Musab AlTurki King Fahd University of Petroleum and Minerals

Étienne André University Paris 13

Toshiaki Aoki JAIST Cyrille Artho AIST

Kyungmin Bae SRI International David Broman KTH and UC Berkeley Bernd Fischer Stellenbosch University

National University of Sciences & Technology Osman Hasan

Klaus Havelund NASA JPL

Fuyuki Ishikawa National Institute of Informatics

Takashi Kitamura AIST

Alexander Knapp Augsburg University Brian Larson Kansas State University Wenchao Li SRI International Robi Malik University of Waikato

Frédéric Mallet Université Nice Sophia Antipolis University of Napoli "Federico II" Roberto Nardone

Thomas Noll RWTH Aachen University

Peter Csaba Ölveczky University of Oslo

Charles Pecheur Université catholique de Louvain

Paul Pettersson Mälardalen University

Camilo Rocha Escuela Colombiana de Ingeniería

Markus Roggenbach Swansea University

Ralf Sasse ETH Zürich

Oleg Sokolsky University of Pennsylvania Sofiène Tahar Concordia University Jean-Pierre Talpin **INRIA** Rennes Chen-Wei Wang McMaster University

Alan Wassyng McMaster University Mike Whalen University of Minnesota Huibiao Zhu

East China Normal University

# **Additional Reviewers**

Ahmed, Waqar Asavoae, Irina Mariuca

Bohórquez, Jaime Cailliau, Antoine Causevic, Adnan Elleuch, Maissa Enoiu, Eduard Paul Filipovikj, Predrag

Gentile, Ugo Guo, Jian

Hachani, Ahmed Inoue, Jun

James, Phillip Khan, Shahid

Limbrée, Christophe Marinescu, Raluca

Matheja, Christoph Nakagawa, Hiroyuki

Seddiki, Ons Siddique, Umair

Su, Wen Sun, Youcheng Wang, Xu Wu, Xi Yokogawa, Tomoyuki Zhang, Min

# Table of Contents

| т  | •  |     | 1 7        | n 1 | 11 |

|----|----|-----|------------|-----|----|

| ın | VI | tec | <b>1</b> 1 | เลเ | ١ĸ |

| Towards Extensible Symbolic Formal Methods                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Real-Time Systems and Statistical Model Checking                                                                                                                                         |

| An Executable Semantics of Clock Constraint Specification Language and its Applications                                                                                                  |

| What's decidable about parametric timed automata?                                                                                                                                        |

| Compositional Predictability Analysis of Mixed Critical Real Time Systems                                                                                                                |

| Abdeldjalil Boudjadar, Juergen Dingel, Boris Madzar and Jin Hyun Kim                                                                                                                     |

| Statistical Model Checking of Simulink Models with Plasma Lab                                                                                                                            |

| Formal Analysis                                                                                                                                                                          |

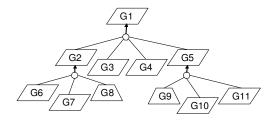

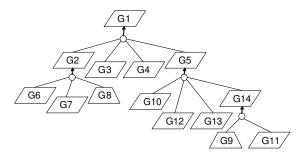

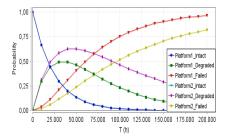

| A Formal Model and Analysis of Feature Degradation in Fault-Tolerant Systems                                                                                                             |

| Towards Verifying VDM using SPIN                                                                                                                                                         |

| Leveraging Abstraction to Establish Out-of-Nominal Safety Properties 87  Jackson R. Mayo, Robert C. Armstrong and Geoffrey C. Hulette                                                    |

| A Concept for Multi-Phase Incremental Formal Verification in Robotic Guided Surgery                                                                                                      |

| Automotive and Avionics Systems                                                                                                                                                          |

| Modeling Safety Requirements of ISO26262 using Goal Trees and Patterns 108  Toshiaki Aoki, Kriangkrai Traichaiyaporn, Yuki Chiba, Masahiro  Matsubara, Masataka Nishi and Fumio Narisawa |

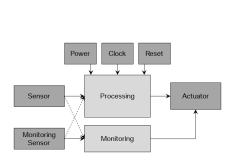

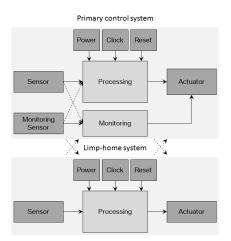

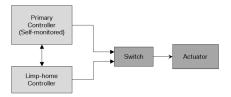

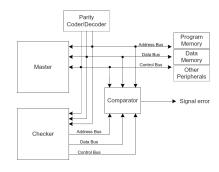

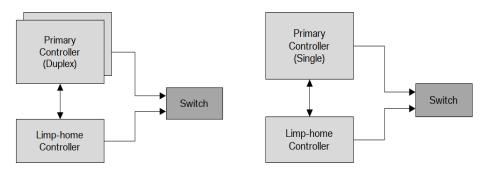

| A Controller Safety Concept based on Software-Implemented Fault Tolerance for Fail-Operational Automotive Applications                                                                   |

| A Formal Approach to Multi-UAV Route Validation                                                                                                                                          |

# Railway Systems

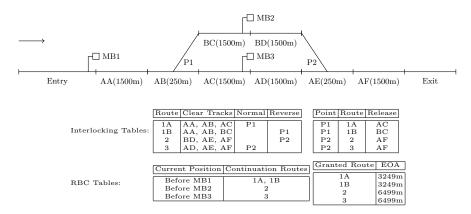

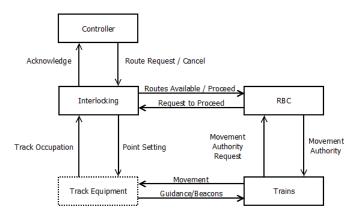

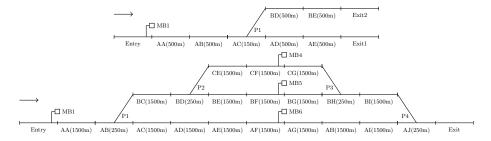

| Towards safety analysis of ERTMS/ETCS Level 2 in Real-Time Maude 14  Phillip James, Andrew Lawrence, Markus Roggenbach and Monika  Seisenberger |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Towards a Body of Knowledge in Formal Methods for the Railway Domain: Identification of Settled Knowledge                                       |

| Modeling Railway Control Systems in Promela                                                                                                     |

| Software, Wireless Networks, and g-HOL                                                                                                          |

| An Approach to Static-Dynamic Software Analysis                                                                                                 |

|                                                                                                                                                 |

| Probabilistic Analysis of a Calculus for Wireless Sensor Networks                                                                               |

# Towards Extensible Symbolic Formal Methods

#### José Meseguer

University of Illinois at Urbana-Champaign

The use of decision procedures for theories axiomatizing data structures and functions commonly occurring in software and hardware systems is currently one of the most effective methods at the heart of state-of-the-art theorem provers and model checkers. It offers the promise, and often even the reality, of scaling up such verification efforts to handle large systems used in industrial practice. In particular, from the model checking perspective a great advantage of using decision procedures is that we can perform infinite-state model checking. This is because we can define infinite sets of states symbolically as states satisfying certain constraints which are formulas whose satisfiability is decidable by some procedure.

But what other symbolic methods are there? And how extensible are they? And how can they be combined? For example, the above model checking and theorem proving methods based on decidable theories supported by an SMT solver extend to combinations of decidable theories supported by the solver (using, for example, the Nelson-Oppen (NO) combination method), but no further. And there is at the moment no straightforward way to combine the symbolic methods of the SMT solver with other symbolic methods. These questions are not academic, but eminently practical: given a formal verification task, the more extensible our symbolic methods are, the more tasks we can automate, and the more can we scale up to solve harder and bigger problems.

A useful distinction between symbolic methods is that they can be either: (i) theory-specific; or (ii) theory-generic. For example, a decision procedure for inequalities between linear polynomials over the real numbers, or a unification algorithm for associative-commutative symbols, are obviously theory-specific. Although theory-specific procedures can be combined by methods like NO, or similar methods to combine unification algorithms, their extensibility cannot go beyond such combinations, and a given tool will only support a finite number of theory-specific procedures. A key advantage of theory-generic methods is that they extend to infinite classes of theories and typically also to their combinations. Another key advantage is that, since their algorithms are generic, their application to a concrete theory becomes user-definable: a tool user, as opposed to a tool implementer, can easily instantiate the generic algorithm to his/her theory of choice, and there are unlimited possibilities for such choices.

In this talk I will:

- 1. briefly review folding variant narrowing for theories satisfying the finite variant property (FVP) as a theory-generic symbolic method for finitary unification modulo the given FVP theory;

- 2. show that folding variant narrowing can be extended under general conditions to a theory-generic SMT solving symbolic method to decide the satis-

- fiability of quantifier-free formulas in the initial algebra of an FVP theory; and

- 3. show how, the recently propose rewriting modulo SMT symbolic model checking method which, until now, was only possible using theory-specific decision procedures, becomes much more widely applicable and extensible thanks to the theory-generic variant-based SMT-solving method described in (2);

- 4. if time permits, I will also summarize theory-generic narrowing-based symbolic model checking methods, and how they can be made even more extensible when combined with the methods described in (1)–(3).

# An Executable Semantics of Clock Constraint Specification Language and its Applications

$\operatorname{Min}$  Zhang<sup>1</sup> and Frédéric  $\operatorname{Mallet}^{2,1,3}$

<sup>1</sup> Shanghai Key Laboratory of Trustworthy Computing Software Engineering Institute, East China Normal University zhangmin@sei.ecnu.edu.cn <sup>2</sup> Univ. Nice Sophia Antipolis, I3S, UMR 7271 CNRS, France Frederic.Mallet@unice.fr <sup>3</sup> INRIA Sophia Antipolis Méditerranée, France

Abstract. The Clock Constraint Specification Language (CCSL) is a language to specify logical and timed constraints between logical clocks. Given a set of clock constraints specified in CCSL, formal analysis is preferred to check if there exists a schedule that satisfies all the constraints, if the constraints are valid or not, and if the constraints satisfy expected properties. In this paper, we present a formal executable semantics of CCSL in rewriting logic and demonstrate some applications of the formal semantics to its formal analysis: 1) to automatically find bounded or periodic schedules that satisfy all the given constraints; 2) to simulate the execution of schedules with customized simulation policies; and 3) to verify LTL properties of CCSL constraints by bounded model checking. Compared with other existing modeling approaches, advantages with the rewriting-based semantics of CCSL are that we do not need to assume a bounded number of steps for the formalization, and we can exhaustively explore all the solutions within a given bound for the analysis.

#### 1 Introduction

Logical time such as defined by Lamport [9] gives a flexible abstraction to compare and order occurrences of events when appealing to more traditional physical measures is either not possible or not desirable. This is the case in a great variety of application domains, from widely distributed systems, for which maintaining a global clock can be costly, to deeply embedded software or in latency-insensitive designs [3], for which the complexity of the control mechanisms (like frequency scaling) makes it neither desirable nor efficient. In the latter case, synchronous languages [2,14] have shown that logical clocks can give a very adequate tool to represent any recurrent event uniformly, whether occurring in a periodic fashion or not.

The Clock Constraint Specification Language (CCSL) [11] is a language that handles logical clocks as first-class citizens. While synchronous languages mainly focus on signals and values and use logical clocks as a controlling mechanism, CCSL discards the values and only focuses on clock-related issues. The formal

operational semantics of CCSL was initially defined in a research report [1] in a bid to provide a reference semantics for building simulation tools, like TimeSquare [6]. We are interested here in studying the properties of a CCSL specification and we give another formal executable semantics in rewriting logic and demonstrate the benefits of this new semantics. The first benefit is that rewriting logic gives a direct implementation of the operational semantics while TimeSquare provides a Java-based implementation, which is prone to introduce accidental complexity.

The second and most important benefit is that we can directly use rewriting logic tooling to model-check a CCSL specification. Previous works on studying CCSL properties [13], rely on several intermediate transformations to automata and other specific formats so that model-checking becomes possible when a CCSL specification is finite (or safe) [12]. It either meant, reducing to a safe subset of CCSL [8] or detecting that the specification was finite even though relying on unsafe operators. In this contribution, we rely on Maude environment [4] to provide a direct analysis support from the operational semantics and we can explore unsafe specifications by using bounded-model checking and do not restrict to the safe subset. While before, successive intermediate transformations could each introduce variations in the semantics, if not careful enough, we rely here on the strong, widely used, generic tooling provided by Maude, rather than on an ad-hoc manual implementation.

More precisely, in this paper, we introduce the notions of bounded and periodic schedules for a CCSL specification. Periodic schedules are useful to reason on specifications that rely on unsafe operators. With periodic schedules, we can use bounded model-checking to verify temporal logic properties on CCSL models. The tooling and automatic verification directly comes with the newly introduced semantics and the Maude environment.

The rest of the paper is organized as follows. Section 2 and Section 3 give a brief introduction to CCSL and Maude. In Section 4 we present the formal definition of semantics of CCSL in Maude, and in Section 5 we demonstrate four applications of the formal semantics to the analysis of CCSL. Section 6 mentions some related work and Section 7 concludes the paper.

#### 2 CCSL

#### 2.1 Syntax and semantics of CCSL

In CCSL, there are four primitive constraint operators which are binary relations between clocks, and five kinds of clock definitions [11]. The four constraint operators are called *precedence*, *causality*, *subclock* and *exclusion*; and the five clock definitions are called *union*, *intersection*, *infimum*, *supremum*, and *delay*.

The meaning of the nine primitive operators (see Fig. 1) is given using the notions of *schedule* and *history*. Given a set C of clocks, a schedule of C is used to decide which clocks can tick at a given step, and a history is used to calculate the number of ticks of each clock at a given step.

**Definition 1 (Schedule).** Given a set C of clocks, a schedule of C is a total function  $\delta: \mathbb{N}^+ \to 2^C$  such that for any n in  $\mathbb{N}^+$ ,  $\delta(n) \neq \emptyset$ .

```

\iff \forall n \in \mathbb{N}^+. \chi(c_1, n) = \chi(c_2, n) \Rightarrow c_2 \notin \delta(n+1)

(Precedence)

\iff \forall n \in \mathbb{N}^+.\chi(c_1,n) \ge \chi(c_2,n)

(Causality)

\iff \forall n \in \mathbb{N}^+.c_1 \in \delta(n) \Rightarrow c_2 \in \delta(n)

(Subclock)

\iff \forall n \in \mathbb{N}^+.c_1 \notin \delta(n) \lor c_2 \notin \delta(n)

(Exclusion)

5. \delta \vDash c_1 \triangleq c_2 + c_3 \iff \forall n \in \mathbb{N}^+ . (c_1 \in \delta(n) \iff c_2 \in \delta(n) \lor c_3 \in \delta(n))

(Union)

6. \delta \vDash c_1 \triangleq c_2 \times c_3 \iff \forall n \in \mathbb{N}^+ . (c_1 \in \delta(n) \iff c_2 \in \delta(n) \land c_3 \in \delta(n))

(Intersection)

7. \delta \models c_1 \triangleq c_2 \land c_3 \iff \forall n \in \mathbb{N}^+.\chi(c_1,n) = max(\chi(c_2,n),\chi(c_3,n))

(Infimum)

8. \delta \models c_1 \triangleq c_2 \lor c_3 \iff \forall n \in \mathbb{N}^+.\chi(c_1,n) = min(\chi(c_2,n),\chi(c_3,n))

(Supremum)

9. \delta \models c_1 \triangleq c_2 \$ d \iff \forall n \in \mathbb{N}^+. \chi(c_1, n) = max(\chi(c_2, n) - d, 0)

(Delay)

```

Fig. 1. Definition of 9 primitive CCSL operators

Note that a schedule must be non-trivial such that there is at least one clock ticking at any execution step. This condition excludes from schedules those steps where no clocks tick. Such steps are called *empty steps* and are trivial in that adding them to a schedule does not affect the logical relations among clocks.

**Definition 2 (History).** A history of a schedule  $\delta : \mathbb{N}^+ \to 2^C$  over a set C of clocks is a function  $\chi : C \times \mathbb{N} \to \mathbb{N}$  such that for any clock  $c \in C$  and  $n \in \mathbb{N}$ :

$$\chi(c,n) = \begin{cases} 0 & \text{if } n = 0\\ \chi(c,n-1) & \text{if } n \neq 0 \land c \notin \delta(n)\\ \chi(c,n-1) + 1 & \text{if } n \neq 0 \land c \in \delta(n) \end{cases}$$

We use  $\delta \vDash \phi$  to denote that schedule  $\delta$  satisfies constraint  $\phi$ . Fig. 1 shows the definition of the satisfiability of a constraint  $\phi$  with regards to a schedule  $\delta$ . We take the definition of precedence for example.  $\delta \vDash c_1 < c_2$  holds if and only if for any n in  $\mathbb{N}$ ,  $c_2$  must not tick at step n+1 if the number of ticks of  $c_1$  is equal to the one of  $c_2$  at step n. Precedence and causality are asynchronous constraints and they forbid clocks to tick depending on what has happened on other clocks in the earlier steps. Subclock and exclusion are synchronous constraints and they force clocks to tick or not depending on whether another clock ticks or not in the same step. Union defines a clock  $c_1$  which ticks whenever  $c_2$  or  $c_3$  ticks; intersection defines a clock  $c_1$  which ticks whenever both  $c_2$  and  $c_3$  tick; supremum defines the slowest clock  $c_1$  which is faster than both  $c_2$  and  $c_3$ ; infimum defines the fastest clock  $c_1$  which is slower than both  $c_2$  and  $c_3$ ; and delay defines the clock  $c_1$  which is delayed by  $c_2$  with d steps. More details can be found in a recent study on CCSL [13].

Given a set  $\Phi$  of clock constraints and a schedule  $\delta$ ,  $\delta$  satisfies  $\Phi$  (denoted by  $\delta \vDash \Phi$ ) if for any  $\phi$  in  $\Phi$  there is  $\delta \vDash \phi$ . In particular, we use  $\delta; k \vDash \phi$  to denote that  $\delta$  satisfies  $\phi$  at step  $k(k \in \mathbb{N}^+)$ . We use  $\delta; k \vDash \Phi$  to denote that  $\delta$  satisfies all the constraints in  $\Phi$  at step k, i.e.,  $\forall \phi \in \Phi$ ,  $\delta; k \vDash \phi$ .

Fig. 2. Periodic schedule

#### 2.2 Satisfiability problem of CCSL

Given a set  $\Phi$  of CCSL constraints, one of the most important problems is to decide if there exist some schedules that satisfy  $\Phi$ . However, it is still an open problem whether the satisfiability of a given arbitrary set of CCSL constraints is decidable or not. We consider two kinds of schedules called *bounded schedule* and *periodic schedule* from the pragmatic point of view and show the satisfiability problem of an arbitrary given set of CCSL constraints with regards to bounded schedule and periodic schedule is decidable.

**Definition 3 (Bounded schedule).** Given a set  $\Phi$  of clock constraints on clocks in C, and a function  $\delta : \mathbb{N}_{\leq n} \to 2^C$ ,  $\delta$  is called an n-bounded schedule if for any  $i \leq n$ ,  $\delta; i \models \Phi$ .

We denote the bounded satisfiability relation by  $\delta \vDash_n \Phi$ , which means that  $\delta$  is an n-bounded schedule of  $\Phi$ . It is obvious that given a bound n it is decidable to check if there exists an n-bounded schedule for a set of CCSL constraints because the number of candidate schedules is finite, i.e.,  $(2^{|C|} - 1)^n$ , where |C| denotes the number of clocks in C. If there does not exist an n-bounded schedule for a set  $\Phi$  of clock constraints, there must not be a schedule that satisfies  $\Phi$ , although not vice versa.

Bounded schedule is sometimes too restrictive in practice because we usually do not assign a bound to clocks in real-time embedded systems, but assume that reactive systems run forever and only terminate when shutdown. Thus, clocks should tick infinite often from the theoretical point of view. There is another class of schedules which are unbounded and force all the clocks to occur periodically. We call them *periodic schedules*.

**Definition 4 (Periodic schedule).** A schedule  $\delta$  is periodic if there exists k, p in  $\mathbb{N}$  such that for any  $k' \geq k$ ,  $\delta(k' + p) = \delta(k')$ .

Figure 2 depicts a periodic schedule whose period is p. Each node denotes a time point, and each arrow denotes the elapse of a time unit. The dashed line indicates that, for any clock, it ticks at one point if and only if it ticks at the other point. From step k, the schedule starts to repeat every p steps infinitely. To decide whether there exists a periodic schedule for a given set of clock constraints is also an open problem. In the rest of this section, we propose an approach to constructing a periodic schedule from a bounded one when the bounded one satisfies certain conditions which are to be introduced below.

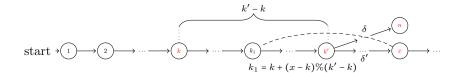

Fig. 3. Construction of periodic schedule  $\delta'$  from an n-bounded schedule  $\delta$

**Lemma 1.** Given a schedule  $\delta : \mathbb{N} \to C$  and two natural numbers k, k', if there exists  $m \in \mathbb{N}$  such that for any c in C  $\chi(c, k) + m = \chi(c, k')$  and  $\chi(c, k+1) + m = \chi(c, k'+1)$  then  $\delta(k+1) = \delta(k'+1)$ .

Proof. It is equal to prove that for any  $c \in C$ ,  $c \in \delta(k+1) \iff c \in \delta(k'+1)$ .  $(\Rightarrow)$ :  $c \in \delta(k+1)$  implies that  $\chi(c,k+1) = \chi(c,k) + 1$ . Thus,  $\chi(c,k+1) + m = \chi(c,k'+1) = \chi(c,k) + 1 + m = \chi(c,k') + 1$ . Thus,  $c \in \delta(k'+1)$ .  $(\Leftarrow)$ :  $c \in \delta(k'+1)$  implies that  $\chi(c,k'+1) = \chi(c,k') + 1$ . Namely,  $\chi(c,k+1) + m = \chi(c,k) + m + 1$ . Thus,  $\chi(c,k+1) = \chi(c,k) + 1$ , and hence we have  $c \in \delta(k+1)$ .

**Theorem 1.** Given a schedule  $\delta : \mathbb{N} \to C$ , a clock constraint  $\phi$ , and two natural numbers  $k, k', \delta; k \models \phi \Rightarrow \sigma; k' \models \phi$  if all the following three conditions are true:

- 1.  $\delta(k) = \delta(k')$ ;

- 2. There exists m in  $\mathbb{N}$  such that m > 0 and for any c in C,  $\chi(c,k) + m = \chi(c,k')$  and  $\chi(c,k+1) + m = \chi(c,k'+1)$ ;

- 3. If  $\phi \equiv (c_1 \triangleq c_2 \$ d), \ \chi(c_2, k) \ge d$ .

Theorem 1 can be proved with Lemma 1. We omit the proof due to the limit of space. From Theorem 1 we can directly derive the following corollary.

**Corollary 1.** Given a schedule  $\delta : \mathbb{N} \to C$ , a set  $\Phi$  of clock constraints, and two natural numbers  $n, k', \delta; k \models \Phi \Rightarrow \sigma; k' \models \Phi$  if the three conditions in Theorem 1 are satisfied.

Given an *n*-bounded schedule  $\delta$  of a set  $\Phi$  of clock constraints, if there exist two natural numbers  $k, k' \leq n$ , which satisfy the three conditions in Theorem 1, we can define a periodic schedule  $\delta'$  based on  $\delta$  such that  $\delta'$  satisfies  $\Phi$ .

$$\delta'(x) = \begin{cases} \delta(x) & \text{if } x \le k' \\ \delta(k + (x - k)\%(k' - k)) & \text{if } x > k' \end{cases}$$

Figure 3 shows the construction of  $\delta'$  based on  $\delta$ . From k', the schedule  $\delta'$  repeats infinitely the steps from k to k'-1. By Corollary 1, it is obvious that for any k'' such that k'' > k', we have  $\delta'; k'' \models \Phi$  because we can find a natural number  $k_1 = k + (k'' - k)\%(k' - k)$  such that  $\delta; k_1 \models \Phi, \delta(k_1) = \delta'(k_1)$  and  $k'', k_1, \delta'$  satisfy the three conditions in Theorem 1. Thus, we have  $\delta' \models \Phi$ .

#### 3 Maude in a Nutshell

Maude is rewriting-based algebraic language and also an efficient rewriting engine. We assume the readers are familiar with Maude, and only give a brief introduction to Maude meta-level functionality and Maude LTL model checking, which is used in this paper. More details about Maude can be found in the Maude book [4].

The underlying logic of Maude is rewriting logic, which is reflective in the sense that it can be faithfully interpreted in itself [4]. The reflectivity allows us to reason with a specified rewrite theory in customized strategies by Maude. Intuitively, we define a rewrite theory  $\mathcal{R}$  and then define a metatheory  $\mathcal{U}$  where  $\mathcal{R}$  is treated as data. A rewrite theory  $\mathcal{R}$  is a tripe  $\langle \Sigma, E, R \rangle$ , where  $\Sigma$  is called the signature specifying the type structure, E is a set of equations and R is a set of rewrite rules. Maude provides efficient function by command search to find if there exist some pathes from a given term t to a target term t' by repeatedly applying the rewrite rules in R. It also provides a corresponding meta-level searching function metaSearch which takes  $\mathcal{R}$ , t and t' as arguments and returns the searching result. An LTL model checker has been implemented based on Maude to verify LTL properties of a rewrite theory when the set of states that are reachable from an initial state in the rewrite theory is finite [7].

#### 4 Formal Semantics of CCSL in Maude

We formalize a clock as a triple  $(c, \ell, n)$ , consisting of the clock identifier c, a list  $\ell$  of records, with each value being tick or idle (abbreviated by t or i respectively), representing that the clock ticks or not at the corresponding step, and a natural number n to indicate the numbers of ticks in  $\ell$ .  $\ell$  represents a bounded schedule of c whose bound is equal to the length of  $\ell$ . Initially,  $\ell$  is empty and n is 0. Let  $\mathcal C$  be the set of such clock triples of a set  $\mathcal C$  of clocks. We call  $\mathcal C$  a configuration. We suppose that the length of the lists in each clock triple in  $\mathcal C$  are equal, e.g. n.  $\mathcal C$  essentially represents an n-bounded schedule for all the clocks in  $\mathcal C$ .

We declare a predicate satisfy which takes three arguments: a configuration  $\mathcal{C}$ , a non-zero natural number k, and a set  $\Phi$  of constraints, and returns true if  $\mathcal{C}$  satisfies  $\Phi$  at step k, and otherwise false. We consider each possible constraint form in  $\Phi$  when defining satisfy. For instance, the following two equations are defined to specify a configuration  $\mathcal{C}$  satisfies precedence and infimum at step k:

The first equation says that satisfy returns true with C, k and  $c_1 < c_2$  when the number of ticks of  $c_1$  up to step k is greater than or equal to the one of  $c_2$  and further if the number of ticks of  $c_1$  up to step k-1 is the same as the one of  $c_2$  then

$c_2$  must not tick at step k (as represented by t-val( $\ell_2,k$ ) =/= t, where t-val is a function returning the  $k^{\rm th}$  value in the list  $\ell_2$ ). The equation has a condition which is a conjunction of two matching equations [4]. The two conjuncts are used to retrieve the tick list and the number of ticks of  $c_1$  (and  $c_2$ ) by function getConf and assign them to  $\ell_1$  and  $n_1$  (and  $\ell_2$  and  $n_2$ ). The second equation defines the semantics of infimum relation, namely, at any step k the number of ticks of  $c_1$  must be the minimum of those of  $c_2$  and  $c_3$ . The correspondence between the formalization of the constraints and their formal semantics defined in Figure 1 should be clear. Other constraints can be formalized in Maude likewise, and we omit them from the paper.

Next we formalize one-step ticking from k to k+1 of all clocks by a set of rewrite rules. The basic idea is as follows. From step k to k+1 each clock decides to tick or not (be idle). After all the clocks make a decision, we check if the bounded schedule satisfies all the constraints at step k+1. The first rewrite rule at Line 1 specifies the behavior that clock c ticks at step k+1. The list  $\ell$  is changed into  $\ell$  t. The rule is conditional because we need the condition that c is not the last clock which makes a decision. If c is the last one, we need to check if all the constraints in  $\Phi$  are satisfied at step k+1. The step k can be represented by the length of the list  $\ell$  of an arbitrary clock triple in C, i.e.,  $k=\mathtt{size}(\ell)$ , where  $\mathtt{size}(\ell)$  returns the length of  $\ell$ . Thus, k+1 is equal to  $\mathtt{size}(\ell)+1$ , and hence we use the latter one in the condition of the fourth equation on Line 6.

Similarly, if c decides to remain idle next step and c is not the last clock, its corresponding tick list is changed from  $\ell$  to  $\ell$  i, which is specified by the rule on Line 2. If c is the last clock in this case, we also need to guarantee that from step k to k+1 there must be at least one clock ticking (represented by the formula not allide(C')) and all the clocks satisfy the constraints in  $\Phi$  at step k+1.

We assume that  $\mathcal{C}$  is a k-bounded schedule of a set  $\Phi$  of CCSL constraints. If there is a rewriting sequence from ( $\mathcal{C}$ ; nil;  $\Phi$ ) to a new one (nil;  $\mathcal{C}'$ ;  $\Phi$ ) with the above four rules,  $\mathcal{C}'$  must be a k+1-bounded schedule of  $\Phi$  because  $\mathcal{C}'$  satisfies  $\Phi$  up to k+1 steps. We can define the following rule to specify the one-step ticking of all the clocks from step k to k+1.

```

1 crl < \mathcal C ; k ; \Phi > => < \mathcal C' ; k +1 ; \Phi > if (\mathcal C ; nil ; \Phi) => (nil ; \mathcal C' ; \Phi) .

```

The condition of the rule is a rewrite condition [4], which is true if and only if there exists a rewriting sequence from the term at the left-hand side of  $\Rightarrow$  to the one at the right-hand side when the condition is true. In the above rule,  $\mathcal{C}'$  represents an arbitrary immediate successor of  $\mathcal{C}$  such that  $\mathcal{C}'$  satisfies  $\Phi$  up to k+1 steps.

#### 5 Applications of the Formal Semantics

In this section, we show four applications of the executable formal semantics of CCSL in Maude.

#### 5.1 Bounded scheduling

Given a bound n and a set of clock constraints  $\Phi$ , we can use Maude's search function to find automatically if there exists an n-bounded schedule of  $\Phi$ . If Maude cannot find a schedule within a given bound n, it means that there must not exist such an n-bounded schedule, and further we can conclude that there must not exist a schedule that satisfies  $\Phi$ . However, if a schedule is found up to bound n, we only can conclude that the returned schedule is n-bounded, but cannot guarantee the existence of a schedule for  $\Phi$ .

We show an example of finding bounded schedules for a given set of clock constraints using Maude's search command.

Example 1. Given a set of constraints  $\Phi_1 = \{c_1 < c_2, c_3 \triangleq c_1 \$ 1, c_2 < c_3, \text{ we can use Maude's search command to find a 100-bounded schedule.}$

Maude's search command takes two optional arguments in the square brackets. The first one is used to specify the number of expected solutions, and the second one is used to specify the maximal depth of searching. Function init takes a set  $\Phi$  of constraints and generates an initial configuration  $<\mathcal{C}_0$ ; 0;  $\Phi>$ , where  $\mathcal{C}_0$  is a set of clock triples, each of which is of the form  $(c, \mathtt{nil}, 0)$ . The operator =>\* indicates there are zero or more rewritings from the given initial term to the expected term that can be matched by the target term.

In this example, the target term represents those configurations where the current step is 200.  $\mathcal{C}$  is a configuration which is assigned by Maude. The result is obtained by repeatedly applying the rewrite rule. Maude only returns one result with the command. It means that there is only one possible 100-bounded schedule for the constraints. The schedule shows that  $c_1$  and  $c_3$  only tick at all odd steps except that  $c_3$  does not tick at the first step, because of the constraint  $c_3 \triangleq c_1 \$ 1$ .  $c_2$  only ticks at all even steps. The returned bounded schedule coincides with the result in an earlier work of the second author [13].

#### 5.2 Customized simulation

Given a set  $\Phi$  of clock constraints, it is also desirable to have a customized schedule which satisfies not only  $\Phi$  but also some customized requirements, e.g., at each step if a clock can tick it must tick, or if a clock does not have to tick, it must not tick. We only consider three basic scheduling policies, called randomness, maximum and minimum respectively.

- Randomness: If a clock can tick and not tick at next step, we randomly choose one.

- Maximum: If a clock can tick at next step, it must tick.

- Minimum: If a clock has not to tick at next step, it must not tick.

Based on the four rewrite rules defined in Section 4, we can achieve customized scheduling for a given set of clock constraints using Maude's meta-level facility. We first find all the possible immediate successors of a set  $\mathcal C$  of clock triples using Maude's metaSearch function, and then choose the successor that satisfies the customized policy given by users. The following rewrite rule is defined for customized scheduling.

```

1 --- the rewrite rule is defined for customized scheduling 2 cr1 < \mathcal{C}; k; \Phi; \rho > => < \mathcal{C}'; k+1; \Phi; \rho > if \mathcal{C}' := conf(sucs(\mathcal{C}, \Phi), \rho) . 3 --- the equation needs the meta-level function metaSearch to compute all successors 4 ceq sucsAux(\mathcal{C}, \Phi, j) = downTerm(T, nil), sucsAux(\mathcal{C}, \Phi, j+1) 5 if RT := metaSearch(upModule('ONE-STEP-TICKING, false), ''(_;;;_')[upTerm(\mathcal{C}), 'nil.Conf, upTerm(\Phi)], ''(_;;;_')['nil.Conf, \mathcal{C}', upTerm(\Phi)], '', ', unbounded, ') /\ 8 (\mathcal{C}' <- T) := getSubstitution(RT) .

```

In the rule,  $\rho$  is a variable, denoting the customized policy given by users, e.g. rand for randomness, max for maximum or min for minimum. The function sucs used in the condition returns the set of all the successors of  $\mathcal C$  that satisfy  $\Phi$ , and conf returns one among them according to the customized policy  $\rho$ . The equation above is used to define a recursive function  $\operatorname{sucsAux}$ , which is the main auxiliary function to define  $\operatorname{sucs}$ . Function  $\operatorname{sucsAux}$  takes three arguments,  $\mathcal C$ ,  $\Phi$  and a natural number j, which indicates that we want  $\operatorname{metaSearch}$  to find the  $j^{\operatorname{th}}(j\geq 0)$  successor of  $\mathcal C$ . The  $\operatorname{metaSearch}$  function takes a meta-module of the module ONE-STEP-TICKING where the four rewrite rules in Section 4 are defined, a term from which searching begins, a target term that the result term can match, and other three arguments, and returns a searching result. The searching result contains a meta-level term which substitute for  $\mathcal C'$ . We change it to the object level by the built-in function downTerm. The object-level term represents the  $i^{\operatorname{th}}$  successor of  $\mathcal C$ . We omit the detailed explanation about the usage of  $\operatorname{metaSearch}$ . Interested readers can refer to the work [4] for the details.

Example 2. Let  $\Phi_2$  be the set of the following constraints:

```

in_1 \leq step_1 step_1 \leq step_3 in_2 \leq step_2

step_2 \leq step_3 step_3 \leq out

```

We show the simulations of the bounded schedules that satisfy  $\Phi_2$  with maximum and minimum policy. We use Maude's **rew** command to rewrite the initial configuration  $< \mathcal{C}_0$ ; 0;  $\Phi$ ;  $\rho >$  by applying the rewrite rule defined in this section 10 times with max and min respectively. The initial configuration is generated by function init1, which takes a set  $\Phi$  of CCSL constraints and a simulation policy  $\rho$  as its arguments. The commands and returned results are shown as follow.

For the first schedule, the number of ticking clocks is always maximal, while for the second one the number of ticking clocks is always minimal.

#### 5.3 Periodic scheduling

We also can find automatically periodic schedules of a given set of CCSL constraints by Maude's search command with the rewriting-based semantics of CCSL in Maude. The basic idea is to compute all possible immediate successors of the current k-bounded schedule at every step  $k(k \ge 1)$  and check if there exists a successor that satisfies all the three conditions in Theorem 1. If such a successor exists, a periodic schedule is found, and the step k+1 is the first step of the second iteration. We also can compute the period of the schedule. The following rewrite rule is defined for periodic scheduling.

The terms at left-hand side of the rule is a 4-tuple, where the last argument, i.e., 0 is indicates that the k-bounded schedule does not satisfy the three conditions in Theorem 1. Function  ${\tt checkOcc}$  is used to check if there exists a k+1-bounded schedule that satisfies all the constraints in  $\varPhi$  and also the three conditions in Theorem 1. If that is the case,  ${\tt checkOcc}$  returns the schedule  $\mathcal{C}''$  and the period p(p>0), and otherwise nil and 0. Once a periodic schedule is found, the rewrite rule cannot be applied and Maude returns the result. Note that the rule may cause non-termination if no periodic schedule is found and no bound to the times of rewriting is set.

As an example, we use Maude's search command to find periodic schedules of the precedence constraint  $c_1 < c_2$ . The command is as follows:

```

1 search [4] init2(c_1 < c_2) =>* < C; k; c_1 < c_2; p > such that p =/= 0 .

```

Function init2 takes a set  $\Phi$  of CCSL constraints and returns an initial configuration  $\langle C_0 \rangle$ ; 0;  $\Phi$ ; 0>, where the last natural number is used to record the

| schedule | clock/step | 1 | 2 | 3 | 4             | 5             | 6 | <br>period $p$ |

|----------|------------|---|---|---|---------------|---------------|---|----------------|

| 1        | $c_1$      | t | t | t | t             | t             | t | <br>1          |

|          | $c_2$      | i | t | t | t             | t             | t | <br>1          |

| 2        | $c_1$      | t | i | t | i             | t             | i | <br>9          |

|          | $c_2$      | i | t | i | t             | i             | t | <br>2          |

| 3        | $c_1$      | t | t | t | t             | t             | t | <br>1          |

|          | $c_2$      | i | i | t | t             | $\mid t \mid$ | t | <br>1          |

| 4        | $c_1$      | t | t | t | i             | t             | i | <br>9          |

|          | $c_2$      | i | i | i | $\mid t \mid$ | i             | t | <br>           |

**Table 1.** Four periodic schedules that satisfy  $c_1 < c_2$

period of the current bounded schedule. We provide an upper bound e.g. 4 to the expected periodic schedules. In the command,  $\mathcal{C}$  is a set of two clock triples of  $c_1$  and  $c_2$  returned by Maude when a periodic schedule is found. k indicates the step where the first period of the schedule ends, and p indicates the period of the schedule. The condition p=/=0 means that  $\mathcal{C}$  represents a periodic schedule. Table 1 shows four periodic schedules found by Maude for  $c_1 < c_2$  when the bound is set 4. The red steps for each schedule are the beginning of the first and second iteration of the period. We also can give p a concrete value and use Maude to search those periodic schedules with a fixed period.

#### 5.4 Bounded model checking

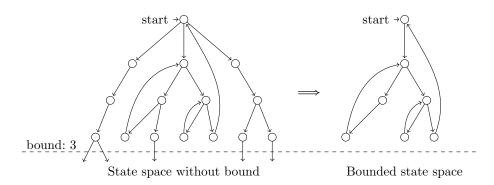

Given a set of clock constraints, it is desired to know if the constraints satisfy some properties, e.g. if all the clocks can tick infinitely often, or a clock must tick immediately after another clock ticks. Based on the formal semantics of CCSL in Maude, we can model check LTL properties of a given set of CCSL constraints by Maude LTL model checker. Maude model checker requires the reachable state space being verified must be finite, while the reachable state space specified by the rewrite theory of a set of clock constraints may be infinite if there exists some non-periodic schedules. For periodic schedules, we force the schedule to repeat from step n to n' where n and n' are the beginning and ending steps of the first period. As depicting by Fig. 4, by setting a bound we can compute all periodic schedules up to the bound. The periodic schedules compose a finite state space which can be used for model checking. Figure 4 (left) shows an example of an unbounded state space. Each path represents a schedule. The path with a loop represents a periodic schedule. There are three periodic schedules in the figure when the bound is set 3. The three periodic schedules constitute a finite state space which can be model checked, as shown in Figure 4 (right).

Next, we show some basic properties that clock constraints are expected to satisfy and their representations in LTL formula. Let tick be a parameterized predicate on states, which takes a clock c as argument and returns true if c ticks in a state and otherwise false.

Fig. 4. Bounded state space of periodic schedulers

- Repeated ticking: all clocks must tick infinitely often, which can be formalized as:  $\bigwedge_{c \in C} \Box \diamondsuit tick(c)$ .

- Simultaneous ticking: two clocks  $c_1$  and  $c_2$  must tick simultaneously, which can be formalized as:  $\Box(tick(c_1) \iff tick(c_2))$ .

- Leading-to ticking: if a clock  $c_1$  ticks, it must cause another clock  $c_2$  to tick eventually, which can be formalized as:  $\Box(tick(c_1) \to \diamondsuit tick(c_2))$ .

- Alternating ticking: two clocks  $c_1$  and  $c_2$  must always tick immediately after each other, which can be formalized as:  $\Box(tick(c_1) \to \bigcirc tick(c_2) \land tick(c_2) \to \bigcirc tick(c_1)$ .

As an example, we model check if the constraints  $\Phi_1$  in Example 1 satisfy the alternating ticking property.

```

1 --- definition of the state predicate tick in Maude 2 ceq <(\mathcal{C}; k; \Phi; p> |= tick(c) = (tval(\ell,k) == t) if (c,\ell,n) := getConf(\mathcal{C}, c) . 3 --- the following command is used for model checking in Maude 4 red modelCheck(init2((c_1 < c_2)(c_3 \stackrel{.}{=} c_1 \stackrel{\$}{$} 1)(c_2 < c_3)), 5 [](tick(c_1) -> 0 tick(c_2) /\ tick(c_2) -> 0 tick(c_1))) . 6 Result: true

```

The first equation is used to define the state predicate tick, and modelCheck is a built-in function to do model checking in Maude. It takes an initial state (configuration) and an LTL formula. Maude returns true with the above command, which means that the constraints  $\Phi_1$  indeed satisfies the alternating ticking property. This result coincides with the one obtained by encoding CCSL into finite-state transition system [13].

By bounded model checking in Maude we also can find invalid schedules of a given set of clock constraints. A schedule is called invalid if it prevent some clock from ticking after some step, namely, it does not satisfy the repeated ticking property. A set  $\Phi$  of CCSL constraints are called invalid if there exist invalid schedules that satisfy  $\Phi$ . Once Maude finds such a periodic schedule that violates the repeated ticking property, we can conclude that the constraints

| No. | $in_1$ | $in_2$ | $step_1$ | $step_2$ | $step_3$ | out   | $tmp_1$ | $tmp_2$ |

|-----|--------|--------|----------|----------|----------|-------|---------|---------|

| 1   | t      | i      | t        | i        | i        | i     | t       | i       |

| 2   | i      | t      | i        | t        | i        | i     | t       | i       |

| 3   | t i    | i $i$  | i t      | i i      | i $i$    | i $i$ | t i     | i $i$   |

| 4   | i $i$  | t $i$  | i $i$    | i t      | i $i$    | i $i$ | t i     | i $i$   |

| 5   | t i t  | t i i  | t i t    | t i i    | i t i    | i t i | t i t   | i i t   |

| 6   | t i i  | t i t  | t i i    | t i t    | i t i    | i t i | t i t   | i i t   |

| 7   | t i t  | t i i  | t i t    | i t i    | i t i    | i t i | t i t   | i i t   |

| 8   | t i i  | t i t  | t i i    | i t t    | i t i    | i t i | t i t   | i i t   |

**Table 2.** Eight deadlock schedules found by Maude for CCSL constraints  $\Phi'_2$

are not valid. However, it cannot grantee the constraints are valid if no invalid schedules are found because not all schedules are model checked.

A special invalid case of CCSL constraints is that some schedules may prevent all clocks from ticking after some step. We call them *deadlock schedules*. We can use Maude to find if there exist deadlock schedules within a given bound. Let us consider a case of Example 2. Assume that we introduce the following four new constraints to  $\Phi_2$  and denote the new set as  $\Phi_2'$ :

$$tmp_1 \triangleq in_1 + in_2$$

$tmp_1 < out$   $tmp_2 \triangleq tmp_1 \$ 1$  out  $tmp_2 \triangleq tmp_1 \$ 1$

The four constraints mean that clocks  $tmp_1$  and out must alternatively tick. We can find a number of schedules satisfying all the constraints in  $\Phi'_2$ . However, some of them may cause deadlock. We find 8 deadlock schedules by searching within 3 steps in Maude with the command:

```

1 search [10,3] init(\Phi_2')=>! \mathcal{CF} .

```

In the command  $\mathcal{CF}$  is a variable to which a 4-tuple is going to be assigned by Maude, and  $\Rightarrow$ ! means that the value assigned to  $\mathcal{CF}$  must be rewritten by any rewrite rules. Namely, the value assigned to  $\mathcal{CF}$  is a deadlock schedule. Table 1 shows the eight deadlock schedules. We take the first one as an example. According to the first schedule, only three clocks, i.e.  $in_1$ ,  $step_1$  and  $tmp_1$  tick at the first step. In next step, no clocks can tick because of the newly introduced four constraints. For instance,  $in_2$  cannot tick in next step. If  $in_2$  ticked, so did  $tmp_1$  (by constraint  $tmp_1 \triangleq in_1 + in_2$ ) and  $tmp_2$  (by constraint  $tmp_2 \triangleq tmp_1 \$ 1$ ), which violates the constraint  $out \prec tmp_2$ . Because  $in_2$  cannot tick,  $step_2$  can neither by constraint  $in_2 \prec step_2$ . Other clocks also cannot tick because of the corresponding constraints, leading to a deadlock.

#### 6 Related Works and discussion

CCSL mainly deals with logical clocks, i.e., unbounded increasing sequences of integers. The semantics of clock constraints may depend on boolean parameters,

in which case, we remain in a finite world and can rely on traditional verification and analysis results and tools. The constraints may also depend on unbounded integer values, for instance, the number of times a given clock has ticked. In this latter case, the constraint is called unsafe [12]. A specification is safe if it does not use any unsafe constraint.

The reference semantics of CCSL was given in a research report [1] mainly to be able to define a simulation tool called TimeSquare [6]. TimeSquare encodes the operational semantics of CCSL in Java and captures boolean constraints symbolically using Binary Decision Diagrams (BDD). TimeSquare works step by step and at each step, finding a solution reduces to a satisfiability problem. After deciding if and how many valid solutions can be found at a step, TimeSquare clock engine picks one solution according to its simulation policy, updates the state space and moves forward. TimeSquare does not consider the unbounded specification as a whole and only produce one finite possible trace that satisfies all the constraints up to a given number of steps. In this work, we use bounded model-checking, we can then explore all the solutions reached in a given number of steps, instead of only one.

Other works have tried to make an exhaustive exploration of the entire state space (not up to a pre-defined number of steps). A comprehensive list of such works has been summarized in a recent survey [13]. However, one aspect is to be able to decide whether the state space can be represented with a finite abstraction even though the specification is unsafe. Another way is to force a finite space space by restricting to safe constraints [16,8,15]. In this work, we do not make any assumptions on whether the specification is safe or not.

The most important achievement in this paper is that, thanks to Maude environment, all the analyses performed result directly from the operational semantics without intermediate transformations, so without the need to prove that the semantics is preserved. Yu et al. proposed to encode CCSL in Signal before transforming it to the internal format of Sigali [16]. We hope that the encoding in Maude will allow to conduct automated verification for all the transformational approaches that use CCSL as a step. Maude also gives a framework to define the simulation policies formally. Some undocumented simulation policies are available in TimeSquare [6]. In Section 4, we give a simple formal interpretation for three of these simulation policies.

Finally, abstract interpretation [5] or infinite model-checking [10] would allow reasoning on the global CCSL specification without restrictions. However, the encoding is likely to introduce semantic variations and we do not know at the moment how to encode CCSL constraints in a compositional way.

#### 7 Conclusion and future work

We have proposed a new semantic model for CCSL constraints. We have also introduced the notion of bounded and periodic schedules. The satisfiability problem for CCSL specifications, which is still an open problem in the general case, is proved to be decidable with regards to bounded and periodic schedules even

when using unsafe constraints. This is the first main result. The second result is to use the MAUDE encoding to perform bounded scheduling, customized simulation with different policies, periodic scheduling, and bounded model-checking.

The notion of periodic schedule seems promising but a bit constraining. In the future, we shall try to provide a more general definition where the behavior might slightly vary between successive periods while still maintaining decidability.

#### References

- André, C.: Syntax and semantics of the Clock Constraint Specification Language (CCSL). Research Report 6925, INRIA (2009)

- Benveniste, A., Caspi, P., Edwards, S.A., Halbwachs, N., Le Guernic, P., de Simone, R.: The synchronous languages 12 years later. Proceedings of the IEEE 91(1), 64– 83 (2003)

- Carloni, L.P., McMillan, K.L., Sangiovanni-Vincentelli, A.L.: Theory of latencyinsensitive design. IEEE Trans. on CAD of Integrated Circuits and Systems 20(9), 1059–1076 (2001)

- 4. Clavel, M., et al.: All about Maude. LNCS 4350, Springer (2007)

- 5. Cousot, P.: Abstract interpretation. ACM Comput. Surv. 28(2), 324–328 (1996)

- Deantoni, J., Mallet, F.: Timesquare: Treat your models with logical time. In: Furia, C.A., Nanz, S. (eds.) TOOLS (50). Lecture Notes in Computer Science, vol. 7304, pp. 34–41. Springer (2012)

- 7. Eker, S., Meseguer, J., Sridharanarayanan, A.: The Maude LTL model checker. In: 4th WRLA, ENTCS 71. pp. 162–187. Elsevier (2002)

- 8. Gascon, R., Mallet, F., DeAntoni, J.: Logical time and temporal logics: Comparing UML MARTE/CCSL and PSL. In: Combi, C., Leucker, M., Wolter, F. (eds.) TIME. pp. 141–148. IEEE (2011)

- 9. Lamport, L.: Time, clocks, and the ordering of events in a distributed system. Commun. ACM 21(7), 558–565 (1978)

- Leroux, J., Sutre, G.: Flat counter automata almost everywhere! In: 3rd International Symposium on Automated Technology for Verification and Analysis. Lecture Notes in Computer Science, vol. 3707, pp. 489–503. Springer (2005)

- Mallet, F., André, C., de Simone, R.: CCSL: specifying clock constraints with UM-L/Marte. Innovations in Systems and Software Engineering 4(3), 309–314 (2008)

- 12. Mallet, F., Millo, J.V., de Simone, R.: Safe CCSL specifications and marked graphs. In: 11th ACM/IEEE Int. Conf. on Formal Methods and Models for Codesign. pp. 157–166. IEEE (2013)

- Mallet, F., de Simone, R.: Correctness issues on MARTE/CCSL constraints. Sci. Comput. Program. 106, 78–92 (2015)

- 14. Potop-Butucaru, D., de Simone, R., Talpin, J.: The Synchronous Hypothesis and Polychronous Languages, chap. 6. CRC Press (2009)

- Yin, L., Mallet, F., Liu, J.: Verification of MARTE/CCSL time requirements in Promela/SPIN. In: Perseil, I., Breitman, K., Sterritt, R. (eds.) ICECCS. pp. 65–74. IEEE Computer Society (2011)

- Yu, H., Talpin, J., Besnard, L., Gautier, T., Marchand, H., Guernic, P.L.: Polychronous controller synthesis from MARTE/CCSL timing specifications. In: 9th IEEE/ACM International Conference on Formal Methods and Models for Codesign, MEMOCODE. pp. 21–30. IEEE (2011)

# What's decidable about parametric timed automata?\*

Étienne André $^{1,2}$

Abstract. Parametric timed automata (PTA) are a powerful formalism to reason, simulate and formally verify critical real-time systems. After two decades of research on PTA, it is now well-understood that any non-trivial problem studied is undecidable for general PTA. We provide here a survey of decision and computation problems for PTA. On the one hand, bounding time, bounding the number of parameters or the domain of the parameters does not (in general) lead to any decidability. On the other hand, restricting the number of clocks, the use of clocks (compared or not with the parameters), and the use of parameters (e. g., used only as upper or lower bounds) leads to decidability of some problems.

#### 1 Introduction

The absence of undesired behaviors in real-time critical systems is of utmost importance in order to ensure the system safety. Model checking aims at formally verifying a model of the system against a correctness property. Timed automata (TA) are a popular formalism to model and verify safety critical systems with timing constraints. TA extend finite state automata with clocks, i. e., real-valued variables increasing linearly [1]. These clocks can be compared with integer constants in guards (sets of linear inequalities that must be satisfied to take a transition) and invariants (sets of linear inequalities that must be satisfied to remain in a location). TA have been widely studied, and several state-of-theart model checkers (such as UPPAAL [28] or PAT [33]) support TA as an input language.

TA benefit from many interesting decidable properties, such as the emptiness of the accepted language, the reachability of a control state, etc. However, TA also suffer from some limitations. First, they cannot be used to specify and verify systems incompletely specified (i. e., whose timing constants are not known yet), and hence cannot be used in early design phases. Second, verifying a system for a set of timing constants usually requires to enumerate all of them one by one if they are supposed to be integer-valued; in addition, TA cannot be used anymore if these constants are rational- or real-valued, and can be taken from a dense

<sup>&</sup>lt;sup>1</sup> Université Paris 13, Sorbonne Paris Cité, LIPN, CNRS, UMR 7030, F-93430, Villetaneuse, France

<sup>&</sup>lt;sup>2</sup> École Centrale de Nantes, IRCCyN, CNRS, UMR 6597, France

<sup>\*</sup> This work is partially supported by the ANR national research program PACS (ANR-14-CE28-0002).

interval. Third, robustness in TA often assumes that all guards can be enlarged or shrinked by the same small variation; considering independent variations or considering both enlarging and shrinking was not addressed, and it is actually unclear whether this can be even considered for TA.

Parametric timed automata (PTA) overcome these limitations by allowing the use of parameters (i. e., unknown constants) in guards and invariants [3]. This increased expressive power comes at the price of the undecidability of most interesting problems – at least in the general case.

Tools such as an extension of UPPAAL [24], ROMÉO [29] or IMITATOR [5] take PTA as input formalism. Beyond the usual academic examples (such as variants of train controllers [3,24]), PTA were also used to successfully specify and verify numerous interesting case studies such as the root contention protocol [24], Philip's bounded retransmission protocol [24], a 4-phase handshake protocol [27], the alternating bit protocol [26], an asynchronous circuit commercialized by ST-Microelectronics [17], (non-preemptive) schedulability problems [26], a distributed prospective architecture for the flight control system of the next generation of spacecrafts designed at ASTRIUM Space Transportation [20], an unmanned aerial video system by Thales, and even analysis of music scores [19].

In this paper, we survey decision problems for PTA proposed in the past two decades. On the one hand, bounding time, bounding the number of parameters or the domain of the parameters does not (in general) lead to any decidability. On the other hand, restricting the number of clocks, the use of clocks (compared or not with the parameters), and the use of parameters (e. g., used only as upper or lower bounds) can lead to the decidability of some problems.

Related Surveys. To the best of our knowledge, no survey was dedicated specifically to decision problems for PTA. In addition, recent results in the field in the past two years (e.g., [16,32,26,10,8]) justify the need for a clear picture of these updated (un)decidability results.

Related works include a work by Henzinger et al. [21], that is not a survey, but exhibits decidable subclasses of hybrid automata, an extension of timed automata where variables can have (in general) arbitrary rates. Then, Asarin et al. proposed a work [9] acting both as a survey and as a contribution paper that studies hybrid automata with "low dimensions", i.e., with few variables. Our survey is also concerned (in Section 4) with decidability results for PTA with few variables (i.e., clocks and parameters). Various problems related to the robustness in TA were also surveyed [12].

Outline. In Section 2, we propose a unified syntax for PTA, and we define the decision problems that we will consider throughout this manuscript. In Section 3, we recall general undecidability for PTA. We then study in Section 4 the decidability when restricting the syntax of PTA (number of variables, syntax of the constraints, etc.). We consider specifically in Section 5 the subclass of L/U-PTA. We conclude by emphasizing open problems in Section 6.

**Table 1:** Syntax of operators in guards

| Operator        | Definition                |  |  |  |

|-----------------|---------------------------|--|--|--|

| ~               | $\{<, \leq, =, \geq, >\}$ |  |  |  |

| <u>&lt;&gt;</u> | $\{\leq,\geq\}$           |  |  |  |

| <>              | {<,>}                     |  |  |  |

| $\preceq$       | {<,≤}                     |  |  |  |

#### 2 Parametric Timed Automata and Problems

#### 2.1 Clocks, Parameters and Constraints

Let  $\mathbb{Z}$ ,  $\mathbb{N}$ ,  $\mathbb{Q}^+$  and  $\mathbb{R}^+$  denote the sets of (possibly negative) integer numbers, (non-negative) natural numbers, non-negative rational numbers, and non-negative real numbers, respectively. In the following,  $\mathbb{T}$  denotes the domain of time, and  $\mathbb{P}$  the domain of the parameters; these domains will be instantiated with  $\mathbb{N}$ ,  $\mathbb{Q}^+$  or  $\mathbb{R}^+$  later on. Throughout this survey, let d denote an integer constant in  $\mathbb{Z}$ , and  $d^+$  denote a non-negative constant in  $\mathbb{N}$ .

Let us assume a set  $X = \{x_1, \ldots, x_H\}$  of *clocks*, that are  $\mathbb{T}$ -valued variables that evolve at the same rate. Let us assume a set  $P = \{p_1, \ldots, p_M\}$  of *parameters*, i. e., unknown constants. A parameter *valuation* v is a function  $v: P \to \mathbb{P}$ . Throughout this survey, symbols  $x, x_i$  denote clocks whereas  $p, p_i$  denote parameters.

A parametric linear term is  $\sum_{1 \leq i \leq M} \alpha_i p_i + d$ , with  $\alpha_i \in \mathbb{Z}$ ; in the following plt will denote a parametric linear term.

A (linear) inequality is  $x \sim plt$ , where x is a clock, plt a parametric linear term, and  $\sim \in \{<, \leq, =, \geq, >\}$ . We give in Table 1 the conventions used throughout this survey concerning comparison operators. A (linear) constraint is a set of linear inequalities.

A simple inequality is either  $x \sim p$  or  $x \sim d^+$ . A simple constraint is a set of simple inequalities.

#### 2.2 A Unified Syntax for Parametric Timed Automata

The syntax of PTA varies a lot in the literature; we give below a definition that includes any definition in the literature. That is, any definition of PTA can be obtained from the following one by adding restrictions such as removing the set of accepting locations, forbidding invariants, restricting the domain of clocks or parameters, simplifying the syntax of the guards and invariants, etc.

**Definition 1.** A PTA is a tuple  $A = (\Sigma, L, l_0, F, X, P, I, E)$ , where:

- $-\Sigma$  is a finite set of actions,

- L is a finite set of locations,

- $-l_0 \in L$  is the initial location,

- $F \subseteq L$  is a set of accepting (or final) locations,

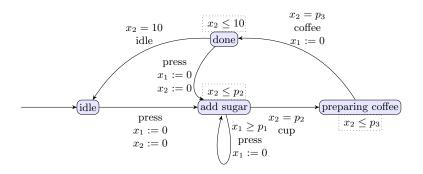

Fig. 1: A coffee machine modeled using a PTA

- X is a set of clocks with domain  $\mathbb{T} = \mathbb{R}^+$ ,

- P is a set of parameters with domain  $\mathbb{P} = \mathbb{R}^+$ ,

- I is the invariant, assigning to every  $l \in L$  a constraint I(l), and

- E is a set of edges (l, g, a, R, l') where  $l, l' \in L$  are the source and destination locations, g is a constraint which is the transition guard,  $a \in \Sigma$ , and  $R \subseteq X$  is a set of clocks to be reset.

Given a PTA A and a parameter valuation v, the valuation of A with v, denoted by v(A), is the (non-parametric) TA where each occurrence of p is replaced with v(p).

We say that a PTA is deterministic if, for any  $l \in L$ , for any  $a \in \Sigma$ , there exists at most one edge  $(l, g, a, R, l') \in E$ , for some g, R, l'. (Note that it differs from a rather common definition of determinism for TA, that allows two or more outgoing transitions with the same action label provided that the corresponding guards are pairwise disjoint.)

A clock is said to be a *parametric clock* if it is compared with at least one parameter in at least one guard or invariant; otherwise, it is a *non-parametric clock*. This notion is central when studying the decidability of problems for PTA with few clocks and parameters.

Example 1. Consider the coffee machine in Fig. 1, modeled using a PTA with 4 locations, 2 clocks  $(x_1 \text{ and } x_2)$  and 3 parameters  $(p_1, p_2, p_3)$ . This PTA is deterministic; both clocks  $x_1$  and  $x_2$  are parametric clocks. The machine can initially idle for an arbitrarily long time. Then, whenever the user presses the (unique) button (action press), the PTA enters location "add sugar", resetting both clocks. The machine can remain in this location as long as the invariant  $(x_2 \leq p_2)$  is satisfied; there, the user can add a dose of sugar by pressing the button (action press), provided the guard  $(x_1 \geq p_1)$  is satisfied, which resets  $x_1$ . That is, the user cannot press twice the button (and hence add two doses of sugar) in a time less than  $p_1$ . Then,  $p_2$  time units after the machine left the idle mode, a cup is delivered (action cup), and the coffee is being prepared; eventually,  $p_2$  time units after the machine left the idle mode, the coffee (action

coffee) is delivered. Then, after 10 time units, the machine returns to the idle mode – unless a user again requests a coffee by pressing the button.

Semantics. The semantics of a PTA A can be defined as the union over all parameter valuations v of the semantics of v(A). In the following, given  $\delta \in \mathbb{R}^+$ ,  $w+\delta$  denotes the valuation such that  $(w+\delta)(x)=w(x)+\delta$ , for all  $x\in X$ . Given  $R\subseteq X$ , we define the reset of a clock valuation w, denoted by  $[w]_R$ , as the valuation resetting the clocks in R, and keeping the other clocks unchanged. Given a parameter valuation v, v(C) denotes the constraint over X obtained by replacing each parameter p in C with v(p). Likewise, given a clock valuation w, w(v(C)) denotes the expression obtained by replacing each clock x in v(C) with w(x). We use the notation w|v|=C to indicate that w(v(C)) evaluates to true.

**Definition 2 (Semantics of a TA).** Given a PTA  $A = (\Sigma, L, l_0, X, P, I, E)$ , and a parameter valuation v, the semantics of v(A) is given by the timed transition system  $(Q, q_0, \Rightarrow)$ , with

```

-Q = \{(l, w) \in L \times \mathbb{R}^{+H} \mid v | w \models I(l) \},

-q_0 = (l_0, X = 0),

```

- $-((l,w),e,(l',w')) \in \Rightarrow if \exists w'' : (l,w) \xrightarrow{e} (l',w'') \xrightarrow{\delta} (l',w'), with:$

- discrete transitions:  $(l, w) \stackrel{e}{\rightarrow} (l', w')$ , if  $(l, w), (l', w') \in Q$ , there exists  $e = (l, g, a, R, l') \in E$ ,  $w' = [w]_R$ , and  $v|w \models g$ ;

- delay transitions:  $(l, w) \stackrel{\delta}{\to} (l, w + \delta)$ , with  $\delta \in \mathbb{R}^+$ , if  $\forall \delta' \in [0, \delta], (l, w + \delta') \in Q$ .

A run of a TA is an alternating sequence of states of Q and edges of the form  $(l_0, w_0) \stackrel{e_0}{\Rightarrow} (l_1, w_1) \stackrel{e_1}{\Rightarrow} \cdots \stackrel{e_{m-1}}{\Rightarrow} (l_m, w_m)$ , such that for all  $i = 0, \dots, m-1$ ,  $e_i \in E$ , and  $((l_i, w_i), e_i, (l_{i+1}, w_{i+1})) \in \Rightarrow$ .

Note that time elapsing can still be a 0-duration  $(d \in \mathbb{R}^+)$  allows d = 0; in other words, TA allow to model Zeno behaviors, i. e., an infinite number of actions within a 0-time or, more generally, a finite time (see e.g., [34]). The accepted timed language is the set of timed words (alternating sequences of actions and time elapsing) associated with an accepting run, i. e., a run ending in a location of F (or, in some works, passing infinitely often by a location in F). Note that some works make a difference between finite and infinite runs. The untimed language of a TA is the timed language projected onto the actions. The set of traces (or trace set) is the set of accepting runs projected onto the locations and actions, i. e., a set of alternating locations and actions.

A symbolic semantics is also defined for PTA as a parametric zone graph [24,4,26], where a symbolic state is made of a discrete part (the current location) and a symbolic, continuous part (a set of diagonal constraints, i. e.,  $x_i - x_j \sim plt$ , sometimes allowing disjunctions).

Simple PTA. We defined simple PTA as the subclass of PTA where guards and invariants are simple constraints. We define this class to show that, even in this restricted situation, all non-trivial problems are undecidable (Section 3).

Variants of the PTA syntax. PTA were first defined in the seminal paper [3] using a set of accepting locations. This is similar to timed automata [1]. Timed Safety Automata (TSA) were introduced later by removing the final states, but adding invariants to locations [23]; many subsequent papers then refer to timed safety automata as simply "timed automata". In contrast, timed automata with accepting locations are often referred to as timed Büchi automata (TBA). It was shown that the timed expressive power of TSA is strictly less than that of TBA [22].

The syntax of PTA differs in most of the papers in the literature. Concerning guards and invariants, in work [3] (resp. [30]), guards (resp. guards and invariants) are conjunctions of inequalities of the form  $x \sim p$ . In work [24,13], guards are conjunctions of inequalities of the form  $x_i - x_j \leq plt \cup \{\infty\}$ ; in work [24] invariants have the same form as guards (invariants are not considered in work [13]). In work [18], guards and invariants are all open, i. e., of the form x < p or  $x < d^+$ . In work [26], guards and invariants are conjunctions of inequalities of the form  $x \sim plt$ , and invariants can only bound clocks from above (i. e.,  $x \leq plt$ ). In work [10], guards are conjunctions of inequalities of the form  $x \sim p$  and invariants can only bound clocks from above (i. e.,  $x \leq p$ ). In work [8], guards and invariants are conjunctions of inequalities of the form  $x \sim p + d$ ,  $x \sim d^+$  or  $p \sim d$  (although the proofs of undecidability only need inequalities of the form  $x \sim p$  or  $x \sim d^+$ ).

A set of accepting locations is considered in several previous works [3,13,10], but only one [13] is interested in infinite accepting runs, i.e., runs that pass infinitely often by an accepting location; hence this latter work considers what could be referred to as parametric timed Büchi automata. In contrast, other previous approaches [24,18,4,26,8] consider parametric timed safety automata (i.e., without accepting locations).

Expressiveness. A comparison of the expressiveness of these different syntactic models remains to be done. Whereas it is likely that allowing constraints of the form  $x \sim plt$  may be simulated using constraints of the form  $x \sim p$  (perhaps adding additional locations, clocks and parameters), the expressiveness may differ when adding a set of accepting locations (just as the timed expressive power of TSA is strictly less than that of TBA [22]). In fact, the expressiveness of a PTA was not even defined; we believe that shall be studied in the future.

#### 2.3 Decision and Computation Problems

We follow here the presentation of a previous approach [26]. Given a class of decision problems  $\mathcal{P}$  (reachability, unavoidability, etc.), let us define the  $\mathcal{P}$ -emptiness, the  $\mathcal{P}$ -universality and the  $\mathcal{P}$ -finiteness. Given a PTA A and an instance  $\phi$  of  $\mathcal{P}$ , the  $\mathcal{P}$ -emptiness,  $\mathcal{P}$ -universality and  $\mathcal{P}$ -finiteness ask whether the set of parameter valuations v such that v(A) satisfies  $\phi$  is empty, is equal to  $\mathbb{P}^{|\mathcal{P}|}$  and is finite, respectively.

In this survey, we mainly focus on reachability and unavoidability properties, and call them EF and AF respectively.<sup>3</sup> We will also mention the EG property, that checks whether there exists a maximal run along which the locations remain in a subset G of the locations, and the AG property that checks whether the locations remain in G for all runs.<sup>4</sup>

Additionally, we will survey the language (resp. trace) preservation (emptiness) problem [8]: given a PTA A and a parameter valuation v, does there exist another valuation  $v' \neq v$  such that the untimed languages (resp. sets of traces) of v(A) and v'(A) are the same?

We finally define the  $\mathcal{P}$ -synthesis problem: Given a PTA A and an instance  $\phi$  of  $\mathcal{P}$ , compute the parameter valuations such that v(A) satisfies  $\phi$ .

Example 2. Let us exemplify some decision and computation problems for the PTA in Fig. 1. Assume the unique target location is "done", i. e.,  $G = \{\text{done}\}$ . EF-emptiness asks whether at least one parameter valuation can reach location "done" for some run; this is true (e. g.,  $p_1 = 1$ ,  $p_2 = 2$ ,  $p_3 = 3$ ). EF-universality asks whether all parameter valuations can reach location "done" for some run; this is false (no parameter valuation such that  $p_2 > p_3$  can reach "done"). AF-emptiness asks whether at least one parameter valuation can reach location "done" for all runs; this is true (e. g.,  $p_1 = 1$ ,  $p_2 = 2$ ,  $p_3 = 3$ ). EF-synthesis consists in synthesizing all valuations for which a run reaches location "done"; the resulting set of valuations is  $0 \le p_2 \le p_3 \le 10 \land p_1 \ge 0$ .

#### 3 Almost Everything is Undecidable for Simple PTA

In this entire section, we consider simple PTA without restriction on the number of clocks and parameters. In that situation, all non-trivial problems studied in the literature are undecidable, with the exception of the membership problem (that asks whether the language of a valuated PTA is empty) – which is rather a problem for TA. By non-trivial, we mean requiring a semantic analysis, and not, e. g., a sole analysis of the syntax of the PTA (e. g., "is the number of clocks even", or any problem defined in Section 2.3 by setting G = L).

We also survey that bounding time (Section 3.3) or the parameter domain for rational-valued parameters (Section 3.4) preserves the undecidability. However, we will show in Section 4 that bounding the number of clocks and/or parameters brings decidability.

All proofs of undecidability reduce from either the halting problem, or the boundedness problem, of a 2-counter machine, known to be undecidable [31].

<sup>&</sup>lt;sup>3</sup> The names EF, AF, EG, AG were first used for PTA by Jovanović *et al.* [26], and come from the CTL syntax.

<sup>&</sup>lt;sup>4</sup> Note that EF-, AF-, EG-, and AG-emptiness are equivalent to AG-, EG-, AF-, EF-universality, respectively.

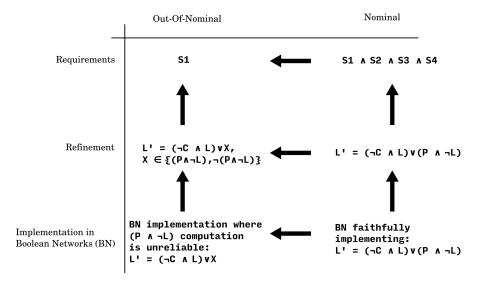

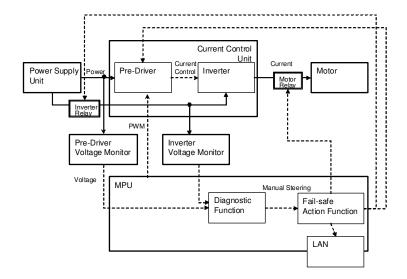

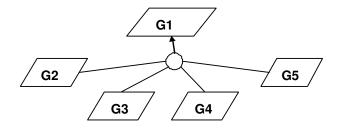

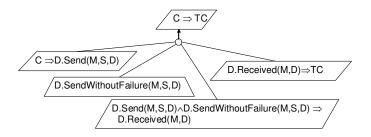

#### 3.1 Decidability of the Membership