Second International Workshop on Formal Techniques for Safety-Critical Systems (FTSCS 2013)

Preliminary Proceedings

Editors: Cyrille Artho and Peter Csaba Ölveczky

# Preface

This volume contains the preliminary proceedings of the *Second International Workshop of Formal Techniques for Safety-Critical Systems* (FTSCS 2013), held in Queenstown, New Zealand, on October 29–30, 2013, as a satellite event of the ICFEM conference.

The aim of this workshop is to bring together researchers and engineers who are interested in the application of formal and semi-formal methods to improve the quality of safety-critical computer systems. FTSCS strives strives to promote research and development of formal methods and tools for industrial applications, and is particularly interested in industrial applications of formal methods. Specific topics include, but are not limited to:

- case studies and experience reports on the use of formal methods for analyzing safety-critical systems, including avionics, automotive, medical, and other kinds of safety-critical and QoS-critical systems;

- methods, techniques and tools to support automated analysis, certification, debugging, etc., of complex safety/QoS-critical systems;

- analysis methods that address the limitations of formal methods in industry (usability, scalability, etc.);

- formal analysis support for modeling languages used in industry, such as AADL, Ptolemy, SysML, SCADE, Modelica, etc.; and

- code generation from validated models.

The workshop received 33 submissions; 32 of these were regular papers and 1 was a work-in-progress/position paper. Each submission was reviewed by three referees; based on the reviews and extensive discussions, the program committee selected 17 regular papers and one work-in-progress paper for presentation at the workshop and inclusion in this volume. In addition, our program also includes an invited talk by Ian Hayes.

Revised versions of accepted regular papers will appear in the post-proceedings of FTSCS 2013 that will be published as a volume in Springer's *Communications in Computer and Information Science* (CCIS) series. Extended versions of selected papers from the workshop will also appear in a special issue of the *Science of Computer Programming* journal.

Many colleagues and friends have contributed to FTSCS 2013. First, we would like to thank Kokichi Futatsugi and Hitoshi Ohsaki for initiating this series of workshops. We thank Ian Hayes for accepting our invitation to give an invited talk and the authors who submitted their work to FTSCS 2013 and who, through their contributions, make this workshop an interesting event. We are particularly grateful that so many well known researchers agreed to serve on the program committee, and that they all provided timely, insightful, and detailed reviews.

We also thank the editors of *Communications in Computer and Information Science* for agreeing to publish the proceedings of FTSCS 2013 as a volume in their series, and Jan A. Bergstra and Bas van Vlijmen for accepting our proposal to devote a special issue of the *Science of Computer Programming* journal to extended versions of selected papers from FTSCS 2013. Furthermore, Jing Sun has been very helpful with the local arrangements. Finally, we thank Andrei Voronkov for the excellent EasyChair conference systems.

We hope that you will all enjoy both the scientific program and the workshop venue!

October, 2013

Cyrille Artho Peter Csaba Ölveczky

# Workshop Organization

# Workshop Chair

Hitoshi Ohsaki AIST

# **Program Chairs**

Cyrille Artho AIST Peter Csaba Ölveczky University of Oslo

# Program Committee

| Erika Abraham<br>Musab Alturki | RWTH Aachen University<br>King Fahd University of Petroleum and Minerals |

|--------------------------------|--------------------------------------------------------------------------|

| Toshiaki Aoki                  | JAIST                                                                    |

| Farhad Arbab                   | Leiden University and CWI                                                |

| Cyrille Artho                  | AIST                                                                     |

| Saddek Bensalem                | Verimag                                                                  |

| Armin Biere                    | Johannes Kepler University                                               |

| Santiago Escobar               | Universidad Politecnica de Valencia                                      |

| Ansgar Fehnker                 | University of the South Pacific                                          |

| Mamoun Filali                  | IRIT                                                                     |

| Bernd Fischer                  | Stellenbosch University/University of Southampton                        |

| Kokichi Futatsugi              | JAIST                                                                    |

| Klaus Havelund                 | NASA JPL/California Institute of Technology                              |

| Marieke Huisman                | University of Twente                                                     |

| Ralf Huuck                     | NICTA                                                                    |

| Fuyuki Ishikawa                | National Institute of Informatics                                        |

| Takashi Kitamura               | AIST                                                                     |

| Alexander Knapp                | Augsburg University                                                      |

| Paddy Krishnan                 | Oracle Labs Brisbane                                                     |

| Yang Liu                       | Nanyang Technological University                                         |

| Robi Malik                     | University of Waikato                                                    |

| Cesar Munoz                    | NASA Langley                                                             |

| Tang Nguyen                    | Hanoi University of Industry                                             |

| Thomas Noll                    | RWTH Aachen University                                                   |

| Peter Ölveczky                 | University of Oslo                                                       |

| Paul Pettersson                | Mälardalen University                                                    |

| Camilo Rocha                   | Escuela Colombiana de Ingenieria                                         |

| Grigore Roşu                   | University of Illinois at Urbana-Champaign                               |

| Neha Rungta        | NASA Ames Research Center   |

|--------------------|-----------------------------|

| Ralf Sasse         | ETH Zürich                  |

| Oleg Sokolsky      | University of Pennsylvania  |

| Sofiene Tahar      | Concordia University        |

| Carolyn Talcott    | SRI International           |

| Tatsuhiro Tsuchiya | Osaka University            |

| Michael Whalen     | University of Minnesota     |

| Peng Wu            | Chinese Academy of Sciences |

# **External Reviewers**

| Daghar, Alaeddine  |

|--------------------|

| Enoiu, Eduard Paul |

| Jansen, Nils       |

| Meredith, Patrick  |

| Santiago, Sonia    |

|                    |

Elleuch, Maissa Helali, Ghassen Kong, Weiqiang Rongjie, Yan

# Table of Contents

| Towards Structuring System Specifications with Time Bands Using<br>Layers of Rely-Guarantee Conditions<br>Ian J. Hayes                                                                 | 1   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Certainly Unsupervisable States<br>Simon Ware, Robi Malik, Sahar Mohajerani and Martin Fabian                                                                                          | 3   |

| Wind Turbine System: An Industrial Case Study in Formal Modeling<br>and Verification                                                                                                   | 19  |

| Precise Documentation and Validation of Requirements<br>Chen-Wei Wang, Jonathan Ostroff and Simon Hudon                                                                                | 35  |

| Reflections on Verifying Software with Whiley<br>David Pearce and Lindsay Groves                                                                                                       | 51  |

| An UPPAAL Framework for Model Checking Automotive Systems<br>with FlexRay Protocol<br>Xiaoyun Guo, Hsin-Hung Lin, Kenro Yatake and Toshiaki Aoki                                       | 67  |

| Early Analysis of Soft Error Effects for Aerospace Applications using<br>Probabilistic Model Checking<br>Khaza Anuarul Hoque, Otmane Ait Mohamed, Yvon Savaria and Claude<br>Thibeault | 83  |

| TTM/PAT: Specifying and Verifying Timed Transition Models<br>Jonathan Ostroff, Chen-Wei Wang, Yang Liu, Jun Sun and Simon<br>Hudon                                                     | 99  |

| On the cloud-enabled refinement checking of railway signalling<br>interlockings                                                                                                        | 115 |

| Counterexample generation for hybrid automata<br>Johanna Nellen, Erika Abraham, Xin Chen and Pieter Collins                                                                            | 131 |

| Compositional Nonblocking Verification with Always Enabled Events<br>and Selfloop-only Events<br><i>Colin Pilbrow and Robi Malik</i>                                                   | 147 |

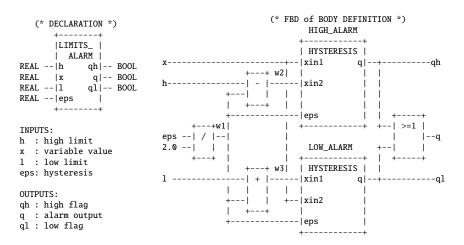

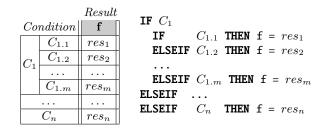

| Formalizing and Verifying Function Blocks using Tabular Expressions<br>and PVS<br>Linna Pang, Chen-Wei Wang, Mark Lawford and Alan Wassyng                                             | 163 |

| Parametric Schedulability Analysis of Fixed Priority Real-Time<br>Distributed Systems                                                                               | 179 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Model Based Testing from Controlled Natural Language Requirements<br>Gustavo Carvalho, Flavia Barros, Florian Lapschies, Uwe Schulze and<br>Jan Peleska             | 195 |

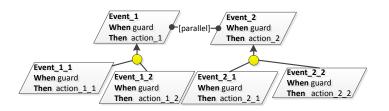

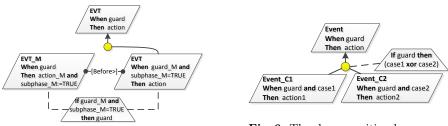

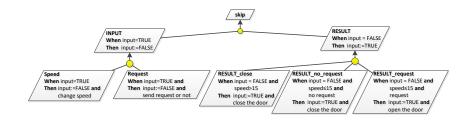

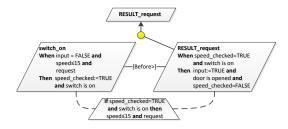

| Refinement Tree and Its Patterns: a Graphical Approach for Event-B<br>Modeling<br><i>Kriangkrai Traichaiyaporn and Toshiaki Aoki</i>                                | 211 |

| Formal Semantics and Analysis of Timed Rebeca in Real-Time Maude<br>Zeynab Sabahi Kaviani, Ramtin Khosravi, Marjan Sirjani, Peter Olveczky<br>and Ehsan Khamespanah |     |

| A Strand Space Approach to Provable Anonymity<br>Yongjian Li and Jun Pang                                                                                           | 243 |

| Creating Visualisations of Formal Models of Interactive Medical Devices .<br>Judy Bowen, Steve Reeves and Steve Jones                                               | 259 |

| With an Open Mind: How to Write Good Models<br>Cyrille Valentin Artho, Koji Hayamizu, Rudolf Ramler and Yoriyuki<br>Yamagata                                        | 264 |

# Towards Structuring System Specifications with Time Bands Using Layers of Rely-Guarantee Conditions

Ian J. Hayes

School of ITEE, The University of Queensland, Brisbane, Australia

Abstract. The overall specification of a cyber-physical system can be given in terms of the desired behaviour of its physical components operating within the real world. The specification of its control software can then be derived from the overall specification and the properties of the real-world phenomena, including their relationship to the computer system's sensors and actuators. The control software specification them becomes a combination of the *guarantee* it makes about the system behaviour and the real-world assumptions it *relies* upon. Such specifications can easily become complicated because the complete system description deals with properties of phenomena at widely different time granularities, as well as handling faults. To help manage this complexity, we consider layering the specification within multiple time bands, with the specification of each time band consisting of both the rely and guarantee conditions for that band, both given in terms of the phenomena of that band. The overall specification is then the combination of the multiple rely-guarantee pairs. Multiple rely-guarantee pairs can also be used to handle faults.

*Rely-guarantee specifications.* Earlier research with Michael Jackson and Cliff Jones [3, 4] looked at specifying real-time control systems in terms of assumptions about the behaviour of the system's environment – a *rely* condition – and the behaviour to be ensured by the system – a *guarantee* condition – provided its environment ensures the rely condition continues to hold. Often the specification of the system's desired behaviour is best described in terms of the behaviour of physical objects in the real-world that are to be controlled by the computer system and rely conditions are needed to link the real-world phenomena (which may not be directly accessible to the computer) to the computer's view of the world, i.e. the computer's sensors and actuators.

*Multiple rely-guarantee pairs.* Our earlier work [4] allowed a specification to be structured into multiple rely-guarantee pairs, where each guarantee is paired with a rely condition expressing the assumptions about the behaviour of the environment needed to be able to achieve that guarantee. This allows one to separate different aspects of the behaviour of a system so that each guarantee is paired with its corresponding rely. It also allows one to separate the specification of "normal" behaviour of the system when the environment is behaving correctly according to the normal rely, and a fall-back or degraded mode of behaviour when the normal rely condition does not hold but a weaker rely does hold.

The time bands framework. Too often when describing of a system's specification (or requirements), the basic operation of the system gets lost in a plethora of low-level detail. For real-time systems it has been observed that it helps to view the system at multiple time bands or scales [1,2]. The phenomena relevant at one time band may be different to those at a finer-grained (lower) time band. The behaviour of a system may be specified by describing aspects of the behaviour separately for each time band in terms of the phenomena of that band. For example, an "instantaneous" event at one time band may correspond to an activity consisting of a set of events (occurring close together) at the next lower time band. Events at the lower time band may be defined in terms of phenomena only "visible" at that time band.

*Rely-guarantee for each time band.* The specification of the behaviour for each time band can be given in terms of a rely condition giving assumed properties of the environment and a guarantee of the behaviour of the system, both in terms of the phenomena of the time band. In this way the behaviour of the overall system is described in terms of multiple rely-guarantee pairs (as described above) with at least one rely-guarantee pair for each time band used in structuring the description of the system behaviour.

*Acknowledgements.* The research presented here is based on joint research with Alan Burns, Brijesh Dongol, Michael Jackson and Cliff Jones. The author's research was supported by Australian Research Council Grants DP0987452 and DP130102901.

# References

- Alan Burns and Gordon Baxter. Time bands in systems structure. In D. Besnard, C. Gacek, and C. B. Jones, editors, *Structure for Dependability: Computer-Based Systems from an Interdisciplinary Perspective*, pages 74–90. Springer, 2006.

- Alan Burns and Ian J. Hayes. A timeband framework for modelling real-time systems. *Real-Time Systems*, 45(1–2):106–142, June 2010.

- 3. I.J. Hayes, M.A. Jackson, and C.B. Jones. Determining the specification of a control system from that of its environment. In K. Araki, S. Gnesi, and D. Mandrioli, editors, *FME 2003: Formal Methods*, volume 2805 of *LNCS*, pages 154–169. Springer Verlag, 2003.

- 4. Cliff B. Jones, Ian J. Hayes, and Michael A. Jackson. Deriving specifications for systems that are connected to the physical world. In Jim Woodcock, editor, *Essays in Honour of Dines Bjørner and Zhou Chaochen on the Occassion of their 70th Birthdays*, volume 4700 of *Lecture Notes in Computer Science*, pages 364–390. Springer Verlag, 2007.

# **Certainly Unsupervisable States**

Simon Ware<sup>1</sup>, Robi Malik<sup>1</sup>, Sahar Mohajerani<sup>2</sup>, and Martin Fabian<sup>2</sup>

<sup>1</sup> Department of Computer Science, University of Waikato, Hamilton, New Zealand {siw4,robi}@waikato.ac.nz

<sup>2</sup> Department of Signals and Systems, Chalmers University of Technology, Gothenburg, Sweden {mohajera,fabian}@chalmers.se

**Abstract.** This paper proposes an abstraction method for compositional synthesis. *Synthesis* is a method to automatically compute a *control program* or *supervisor* that restricts the behaviour of a given system to ensure safety and liveness. *Compositional synthesis* uses repeated abstraction and simplification to combat the state-space explosion problem for large systems. The abstraction method proposed in this paper finds and removes the so-called *certainly unsupervisable* states. By removing these states at an early stage, the final state space can be reduced substantially. The paper describes an algorithm with cubic time complexity to compute the largest possible set of removable states. A practical example demonstrates the feasibility of the method to solve real-world problems.

# 1 Introduction

*Reactive systems* are used extensively to control safety-critical applications, where a small error can result in huge financial or human losses. With their size and complexity continuously increasing, there is an increasing demand for formal modelling and analysis. *Model checking* [4] has been used successfully to automatically detect errors in reactive systems. In some cases, it is possible to go further and *synthesise*, i.e., automatically compute a controlling agent that removes certain kinds of errors from a system.

The controller synthesis problem has been studied by several researchers in computing and control. The synthesis of a stand-alone controller from a temporal logic specification is studied in [7, 19]. Synthesis has been generalised to the extraction of an environment to interact with a given software *interface* [1], and to the construction controllers interacting with a given *environment* or *plant* [2,5]. *Supervisory control theory* [20] of discrete event systems provides a framework to synthesise a *supervisor* that restricts the behaviour of a given plant as little as possible while ensuring the safety and liveness properties of *controllability* and *nonblocking*.

Straightforward synthesis algorithms explore the complete *monolithic* state space of the system, and are therefore limited by the well-known *state-space explosion* problem. The sheer size of the supervisor also makes it humanly incomprehensible, which hinders acceptance of the synthesis approach in industrial settings. These problems are addressed by *compositional* methods [3,8]. If a temporal logic specification is the conjunction of several requirements, it is possible to synthesise separate controller components

for each requirement [5, 7]. Compositional approaches in supervisory control [9, 16] exploit the structure of the model of the plant to be controlled, which typically consists of several interacting components. These approaches avoid constructing the full state space by first simplifying individual components, then applying synchronous composition step by step, and simplifying the intermediate results again.

This kind of compositional synthesis requires specific abstraction methods to guarantee a least restrictive, controllable, and nonblocking final synthesis result. *Supervision equivalence* [9] and *synthesis abstraction* [16] have been proposed for this purpose, and several abstraction methods to simplify automata preserving these properties are known.

This paper proposes another abstraction method that can be used in compositional synthesis frameworks such as [9, 16]. The proposed method finds all the states that will certainly be removed by any supervisor. Removing these so-called *certainly unsupervisable states* at an early stage reduces the state space substantially. Previously, *halfway synthesis* [9] was used for this purpose, which approximates the removable states. The set of certainly unsupervisable states is the largest possible set of removable states, and it can be computed in the same cubic complexity as halfway synthesis.

This paper is organised as follows. Section 2 introduces the terminology of supervisory control theory [20] and the framework of compositional synthesis [9, 16]. Next, Section 3 explains the ideas of compositional synthesis and certainly unsupervisable states using the example of a manufacturing system. Section 4 presents the results of this paper: it defines the set of certainly unsupervisable states, gives an algorithm to compute it, performs complexity analysis, and compares certainly unsupervisable states to halfway synthesis. Finally, Section 5 adds some concluding remarks.

# 2 Preliminaries

#### 2.1 Events and Languages

Discrete event systems are modelled using events and languages [20]. *Events* represent incidents that cause transitions from one state to another and are taken from a finite alphabet  $\Sigma$ . For the purpose of supervisory control, the alphabet is partitioned into two disjoint subsets, the set  $\Sigma_c$  of *controllable* events and the set  $\Sigma_u$  of *uncontrollable* events. Controllable events can be disabled by a supervising agent, while uncontrollable events occur spontaneously. In addition, the *silent controllable* event  $\tau_c \in \Sigma_c$  and the *silent uncontrollable* event  $\tau_u \in \Sigma_u$  denote transitions that are not taken by any component other than the one being considered. The set of all finite *traces* of events from  $\Sigma$ , including the *empty trace*  $\varepsilon$ , is denoted by  $\Sigma^*$ . A subset  $L \subseteq \Sigma^*$  is called a *language*. The *concatenation* of two traces  $s, t \in \Sigma^*$  is written as *st*.

#### 2.2 Nondeterministic Automata

System behaviours are typically modelled by deterministic automata, but nondeterministic automata may arise as intermediate results during abstraction.

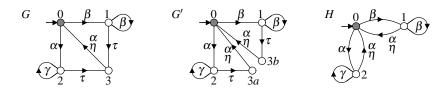

**Definition 1.** A (nondeterministic) finite automaton is a tuple  $G = \langle \Sigma, Q, \rightarrow, Q^{\circ}, Q^{\omega} \rangle$ , where  $\Sigma$  is a finite set of events, Q is a finite set of *states*,  $\rightarrow \subseteq Q \times \Sigma \times Q$  is the *state*

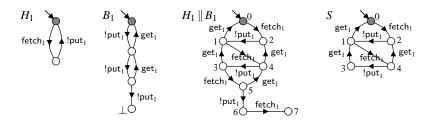

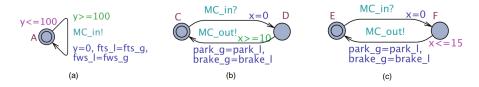

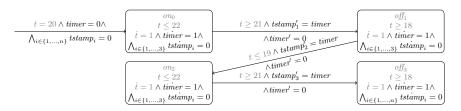

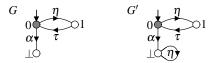

Fig. 1. Simple manufacturing system. Events  $fetch_1$  and  $get_1$  are controllable, while  $!put_1$  is uncontrollable.

*transition relation*,  $Q^{\circ} \subseteq Q$  is the set of *initial states*, and  $Q^{\omega} \subseteq Q$  is the set of *accepting states*. *G* is *deterministic* if  $|Q^{\circ}| \leq 1$  and  $\tau_{u}, \tau_{c} \notin \Sigma$ , and for all transitions  $x \xrightarrow{\sigma} y_{1}$  and  $x \xrightarrow{\sigma} y_{2}$  it holds that  $y_{1} = y_{2}$ .

The transition relation is written in infix notation  $x \xrightarrow{\sigma} y$ , and is extended to traces and languages in the standard way. For example,  $x \xrightarrow{\tau_u^* \sigma} y$  means that there exists a possibly empty sequence of  $\tau_u$ -transitions followed by a  $\sigma$ -transition that leads from state *x* to *y*. Furthermore,  $x \xrightarrow{s}$  means  $x \xrightarrow{s} y$  for some  $y \in Q$ , and  $x \to y$  means  $x \xrightarrow{s} y$ for some  $s \in \Sigma^*$ . These notations also apply to state sets and to automata:  $X \xrightarrow{s} Y$  for  $X, Y \subseteq Q$  means  $x \xrightarrow{s} y$  for some  $x \in X$  and  $y \in Y$ , and  $G \xrightarrow{s} x$  means  $Q^\circ \xrightarrow{s} x$ .

**Example 1.** Fig. 1 shows automata models of a simple manufacturing system consisting of a handler  $H_1$  and a buffer  $B_1$ . The handler fetches a workpiece (fetch<sub>1</sub>) and then puts it into the buffer (!put<sub>1</sub>). The event !put<sub>1</sub> also increases the number of workpieces in the buffer by 1. Afterwards the buffer can release the workpiece (get<sub>1</sub>), reducing the number of workpieces in the buffer by 1. The buffer by 1. The buffer can store only two workpieces, adding more workpieces causes overflow as represented by the state  $\perp$ .

**Definition 2.** Let  $G_1 = \langle \Sigma_1, Q_1, \rightarrow_1, Q_1^{\circ}, Q_1^{\omega} \rangle$  and  $G_2 = \langle \Sigma_2, Q_2, \rightarrow_2, Q_2^{\circ}, Q_2^{\omega} \rangle$  be two automata. The synchronous composition of  $G_1$  and  $G_2$  is

$$G_1 \parallel G_2 = \langle \Sigma_1 \cup \Sigma_2, Q_1 \times Q_2, \rightarrow, Q_1^{\circ} \times Q_2^{\circ}, Q_1^{\omega} \times Q_2^{\omega} \rangle \tag{1}$$

where

$$- (x_1, x_2) \xrightarrow{\sigma} (y_1, y_2), \text{ if } \sigma \in (\Sigma_1 \cap \Sigma_2) \setminus \{\tau_u, \tau_c\}, x_1 \xrightarrow{\sigma}_1 y_1, \text{ and } x_2 \xrightarrow{\sigma}_2 y_2; \\ - (x_1, x_2) \xrightarrow{\sigma} (y_1, x_2), \text{ if } \sigma \in (\Sigma_1 \setminus \Sigma_2) \cup \{\tau_u, \tau_c\} \text{ and } x_1 \xrightarrow{\sigma}_1 y_1; \\ - (x_1, x_2) \xrightarrow{\sigma} (x_1, y_2), \text{ if } \sigma \in (\Sigma_2 \setminus \Sigma_1) \cup \{\tau_u, \tau_c\} \text{ and } x_2 \xrightarrow{\sigma}_2 y_2.$$

Automata are synchronised in lock-step synchronisation [11]. Shared events must be executed by all automata together, while events used by only one automaton (and the silent events  $\tau_u$  and  $\tau_c$ ) are executed by only that automaton. Fig. 1 shows the synchronous composition  $H_1 || B_1$  of the automata mentioned in Example 1.

Another common operation in compositional synthesis is *hiding*, which removes the identity of certain events and in general produces a nondeterministic automaton.

**Definition 3.** Let  $G = \langle \Sigma, Q, \rightarrow, Q^{\circ}, Q^{\omega} \rangle$  be an automaton and  $\Upsilon \subseteq \Sigma$ . The result of *controllability preserving hiding* of  $\Upsilon$  from *G* is  $G \setminus_! \Upsilon = \langle \Sigma \setminus \Upsilon, Q, \rightarrow_!, Q^{\circ}, Q^{\omega} \rangle$ , where  $\rightarrow_!$  is obtained from  $\rightarrow$  by replacing each transition  $x \xrightarrow{\sigma} y$  such that  $\sigma \in \Upsilon$  by  $x \xrightarrow{\tau_c} y$  if  $\sigma \in \Sigma_c$  or by  $x \xrightarrow{\tau_u} y$  if  $\sigma \in \Sigma_u$ .

#### 2.3 Supervisory Control Theory

*Supervisory control theory* [20] provides a means to automatically compute so-called *supervisors* that control a given system to perform some desired functionality. Given an automaton model of the possible behaviour of a physical system, called the *plant*, a supervisor is sought to restrict the behaviour in such a way that only a certain subset of the state space is reachable. The supervisor is implemented as a *control function* [20]

$$\Phi: Q \to 2^{\Sigma \times Q} \tag{2}$$

that assigns to each state  $x \in Q$  the set  $\Phi(x)$  of transitions to be enabled in this state. That is, a transition  $x \xrightarrow{\sigma} y$  with  $\sigma \in \Sigma_c$  will only be possible under the control of supervisor  $\Phi$ if  $(\sigma, y) \in \Phi(x)$ . Uncontrollable events cannot be disabled, so it is required that  $\Sigma_u \times Q \subseteq \Phi(x)$  for all  $x \in Q$ . Controllable transitions can be disabled individually, i.e., if a nondeterministic system contains multiple outgoing controllable transitions from a state *x*, then the supervisor may disable some of them while leaving others enabled [9]. If the plant is modelled by a nondeterministic automaton, then such a supervisor can be represented as a *subautomaton*.

**Definition 4.** [9] Let  $G = \langle \Sigma, Q_G, \rightarrow_G, Q_G^{\circ}, Q_G^{\omega} \rangle$  and  $K = \langle \Sigma, Q_K, \rightarrow_K, Q_K^{\circ}, Q_K^{\omega} \rangle$  be two automata. *K* is a *subautomaton* of *G*, written  $K \subseteq G$ , if  $Q_K \subseteq Q_G, \rightarrow_K \subseteq \rightarrow_G, Q_K^{\circ} \subseteq Q_G^{\circ}$ , and  $Q_K^{\omega} \subseteq Q_G^{\omega}$ .

A subautomaton K of G contains a subset of the states and transitions of G. It represents a supervisor that enables only those transitions present in K, i.e., it implements the control function

$$\Phi_K(x) = (\Sigma_{\mathbf{u}} \times Q) \cup \{ (\sigma, y) \in \Sigma_{\mathbf{c}} \times Q \mid x \xrightarrow{o}_K y \}.$$

(3)

As uncontrollable events cannot be disabled, the control function includes all possible uncontrollable transitions. Then not every subautomaton of G can be implemented through control. The property of *controllability* [20] characterises those behaviours than can be implemented.

**Definition 5.** [9] Let  $G = \langle \Sigma, Q_G, \rightarrow_G, Q_G^{\circ}, Q_G^{\omega} \rangle$  and  $K = \langle \Sigma, Q_K, \rightarrow_K, Q_K^{\circ}, Q_K^{\omega} \rangle$  such that  $K \subseteq G$ . Then *K* is called *controllable* in *G* if, for all states  $x \in Q_K$  and  $y \in Q_G$  and for every uncontrollable event  $v \in \Sigma_u$  such that  $x \stackrel{v}{\rightarrow}_G y$ , it also holds that  $x \stackrel{v}{\rightarrow}_K y$ .

If a subautomaton K is controllable in G, then every uncontrollable transition possible in G is also contained in K. In Fig. 1, automaton S is controllable in  $H_1 || B_1$ . However, if state 5 was to be included in S, then because of the uncontrollable transition

$5 \xrightarrow{!put_1} 6$ , state 6 would also have to be included for *S* to be controllable. Controllability ensures that the control function (3) can be implemented without disabling any uncontrollable events.

In addition to controllability, the supervised behaviour is typically required to be *nonblocking*.

**Definition 6.** [15] Let  $G = \langle \Sigma, Q, \rightarrow, Q^{\circ}, Q^{\omega} \rangle$  be an automaton. *G* is called *nonblock-ing* if for every state  $x \in Q$  such that  $Q^{\circ} \rightarrow x$  it holds that  $x \rightarrow Q^{\omega}$ .

In a nonblocking automaton, termination is possible from every reachable state. The nonblocking property, also referred to as *weak termination* [17], ensures the absence of livelocks and deadlocks. Combined with controllability, the requirement to be nonblocking can express arbitrary safety properties [9]. For example, the buffer model  $B_1$  in Fig. 1 contains the !put<sub>1</sub>-transition to the blocking state  $\perp$  to specify a supervised behaviour that does not allow a third workpiece to be placed into the buffer when it already contains two workpieces, i.e., it requests a supervisor that prevents buffer overflow.

Given a plant automaton *G*, the objective of *supervisor synthesis* [20] is to compute a subautomaton  $K \subseteq G$ , which is controllable and nonblocking and restricts the behaviour of *G* as little as possible. The set of subautomata of *G* forms a lattice [6], and the upper bound of a set of controllable and nonblocking subautomata in this lattice is again controllable and nonblocking.

**Theorem 1.** [9] Let  $G = \langle \Sigma, Q, \to, Q^{\circ}, Q^{\omega} \rangle$  be an automaton. There exists a unique subautomaton  $\sup \mathscr{C}(G) \subseteq G$  such that  $\sup \mathscr{C}(G)$  is nonblocking and controllable in *G*, and such that for every subautomaton  $S \subseteq G$  that is also nonblocking and controllable in *G*, it holds that  $S \subseteq \sup \mathscr{C}(G)$ .

The subautomaton  $\sup \mathcal{C}(G)$  is the unique *least restrictive* sub-behaviour of *G* that can be achieved by any possible supervisor. It can be computed using a fixpoint iteration [9], by iteratively removing blocking states and states leading to blocking states via uncontrollable events, until a fixpoint is reached.

**Definition 7.** [9] Let  $G = \langle \Sigma, Q, \to, Q^{\circ}, Q^{\omega} \rangle$  be an automaton. The *restriction* of *G* to  $X \subseteq Q$  is  $G_{|X} = \langle \Sigma, X, \to_{|X}, Q^{\circ} \cap X, Q^{\omega} \cap X \rangle$ , where  $\to_{|X} = \{ (x, \sigma, y) \in \to | x, y \in X \}$ .

**Definition 8.** [9] Let  $G = \langle \Sigma, Q, \to, Q^{\circ}, Q^{\omega} \rangle$  be an automaton. The *synthesis step* operator  $\Theta_G \colon 2^Q \to 2^Q$  for G is defined as  $\Theta_G(X) = \Theta_G^{\text{cont}}(X) \cap \Theta_G^{\text{cont}}(X)$ , where

$$\Theta_G^{\text{cont}}(X) = \{ x \in X \mid \text{for all transitions } x \xrightarrow{b} y \text{ with } v \in \Sigma_u \text{ it holds that } y \in X \}; \quad (4)$$

$$\Theta_G^{\text{nonb}}(X) = \{ x \in X \mid x \to_{|X} Q^{\omega} \}. \quad (5)$$

$\Theta_G^{\text{cont}}$  captures controllability, and  $\Theta_G^{\text{nonb}}$  captures nonblocking. The least restrictive synthesis result  $\sup \mathscr{C}(G)$  is obtained by restricting *G* to the greatest fixpoint of  $\Theta_G$ .

**Theorem 2.** [9] Let  $G = \langle \Sigma, Q, \rightarrow, Q^{\circ}, Q^{\omega} \rangle$ . The synthesis step operator  $\Theta_G$  has a greatest fixpoint gfp $\Theta_G = \hat{\Theta}_G \subseteq Q$ , such that  $G_{|\hat{\Theta}_G}$  is the greatest subautomaton of *G* that is both controllable in *G* and nonblocking, i.e.,

$$\sup \mathscr{C}(G) = G_{|\hat{\Theta}_G} . \tag{6}$$

**Example 2.** The automaton  $H_1 || B_1$  in Fig. 1 is blocking, because the trace fetch<sub>1</sub>!put<sub>1</sub> fetch<sub>1</sub>!put<sub>1</sub> leads to state 6, from where no accepting state is reachable. To prevent this blocking situation, event !put<sub>1</sub> needs to be disabled in state 5. However, !put<sub>1</sub> is an uncontrollable event that cannot be disabled by the supervisor, so the best feasible solution is to disable the controllable event fetch<sub>1</sub> in state 3. Fig. 1 shows the least restrictive supervisor  $S = \sup \mathcal{C}(H_1 || B_1)$ .

In the finite-state case, the state set of the least restrictive supervisor can be calculated as the limit of the sequence  $X^0 = Q$ ,  $X^{i+1} = \Theta_G(X^i)$ . This iteration converges in at most |Q| iterations, and the worst-case time complexity is  $O(|Q|| \rightarrow |) = O(|\Sigma||Q|^3)$ , where  $|\Sigma|$ , |Q|, and  $|\rightarrow|$  are the numbers of events, states, and transitions of the plant automaton *G*. However, often the behaviour the system is specified by a large number of synchronised automata, and when measured by the number of components, the synthesis problem is NP-complete [10].

#### 2.4 Compositional Synthesis

Many discrete event systems are *modular* in that they consist of a large number of interacting components. This modularity allows to simplify individual components before composing them, in many cases avoiding state-space explosion. This idea has been used successfully for verification of large discrete event systems [8].

Given a system of concurrent plant automata

$$\mathscr{G} = G_1 \parallel G_2 \parallel \cdots \parallel G_n , \qquad (7)$$

the objective of synthesis is to find a least restrictive supervisor, which ensures nonblocking without disabling uncontrollable events. The standard solution [20] to this problem is to calculate a finite-state representation of the synchronous composition (7) and use a synthesis iteration to calculate  $\sup \mathscr{C}(\mathscr{G}) = \sup \mathscr{C}(G_1 \| \cdots \| G_n)$ .

A compositional algorithm tries to find the same result without explicitly calculating the synchronous product (7). It seeks to abstract individual automata  $G_i$  by removing some states or transitions, and replace them by abstracted versions  $\tilde{G}_i$ . If no more abstraction is possible, synchronous composition is computed step by step, abstracting the intermediate results again.

The individual automata  $G_i$  typically contain some events that do not appear in any other automata  $G_j$ . These events are called *local* events, denoted by the set  $\Upsilon$  in the following. After hiding the local events, the automaton  $G_i$  is replaced by  $G_i \setminus \Upsilon$ , which increases the possibility of further abstraction.

Eventually, the procedure leads to a single automaton  $\tilde{G}$ , the abstract description of the system  $\mathscr{G}$ . After abstraction, the automaton of  $\tilde{G}$  has less states and transitions compared to (7). Once  $\tilde{G}$  is found, the final step is to use it instead of the original system, to obtain a synthesis result  $\sup \mathscr{C}(\tilde{G}) = \sup \mathscr{C}(\mathscr{G})$ .

The abstraction steps to simplify the individual automata  $G_i$  must satisfy certain conditions to guarantee that the synthesis result obtained from the final abstraction is a correct supervisor for the original system.

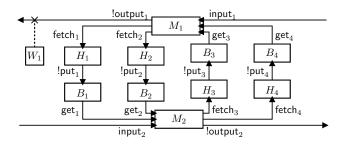

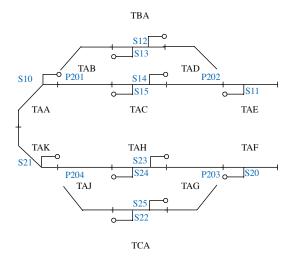

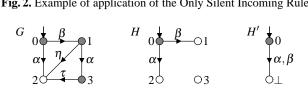

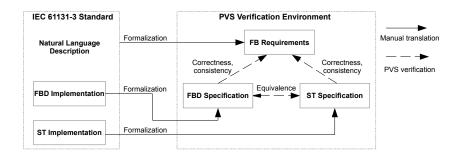

Fig. 2. Manufacturing system overview.

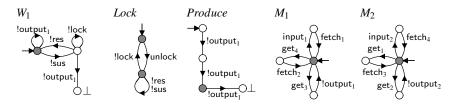

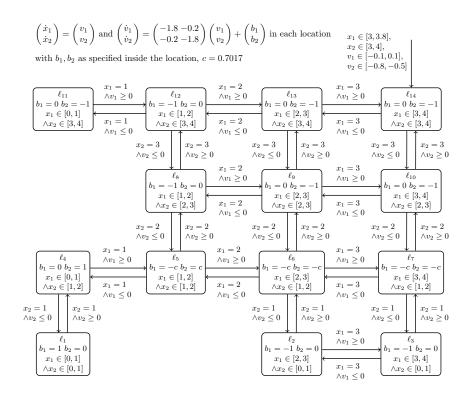

Fig. 3. Automata for manufacturing system model. Uncontrollable events are prefixed by !.

**Definition 9.** Let *G* and *H* be two automata with alphabet  $\Sigma$ . Then *G* is a *synthesis* equivalent to *H*, written  $G \simeq_{\text{synth}} H$ , if for every automaton  $T = \langle \Sigma_T, Q_T, \rightarrow_T, Q_T^{\circ}, Q_T^{\omega} \rangle$  it holds that  $\sup \mathscr{C}(G || T) = \sup \mathscr{C}(H || T)$ .

Def. 9 is a special case of synthesis abstraction [16]. Synthesis equivalence requires that the abstracted automaton H yields the same supervisor as the original automaton G, no matter what the remainder of the system T is.

## 3 Manufacturing System Example

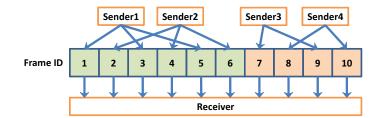

This section demonstrates compositional synthesis using a modified version of a manufacturing system previously studied in [13]. The manufacturing system consists of two machines ( $M_1$  and  $M_2$ ) and four pairs of handlers ( $H_i$ ) and buffers ( $B_i$ ) for transferring workpieces between the machines. Fig. 2 gives an overview of the system.

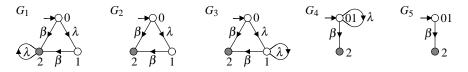

The manufacturing system can produce two types of workpieces. Type I workpieces are first processed by machine  $M_1$  (input<sub>1</sub>). Then they are fetched by handler  $H_1$  (fetch<sub>1</sub>) and placed into buffer  $B_1$  (!put<sub>1</sub>). Next, they are processed by  $M_2$  (get<sub>1</sub>), fetched by  $H_4$ (fetch<sub>4</sub>) and placed into  $B_4$  (!put<sub>4</sub>). Finally, they are processed by  $M_1$  once more (get<sub>4</sub>), and released (!output<sub>1</sub>). Using a switch  $W_1$ , users can request to suspend (!sus) or resume (!res) production of  $M_1$ , provided that the switch has been unlocked (unlock) by the system. Type II workpieces are first processed by  $M_2$ , passed through  $H_3$  and  $B_3$ , further processed by  $M_1$ , passed through  $H_2$  and  $B_2$ , and finally processed by  $M_2$ . The handlers and buffers are modelled as in Fig. 1, and Fig. 3 shows the rest of the automata model of the system. Automata  $W_1$  and *Produce* use the blocking states  $\perp$  to model requirements for the synthesised supervisor to prevent output from  $M_1$  in suspend mode and to produce exactly two Type I workpieces.

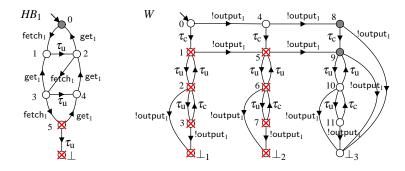

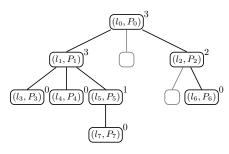

Fig. 4. Automata encountered during compositional synthesis of manufacturing system example.

In the following, compositional synthesis is used to synthesise a supervisor subject to these requirements. Initially, the system is

$$\mathscr{G} = M_1 \| M_2 \| Lock \| Produce \| H_1 \| B_1 \| \cdots \| H_4 \| B_4 .$$

(8)

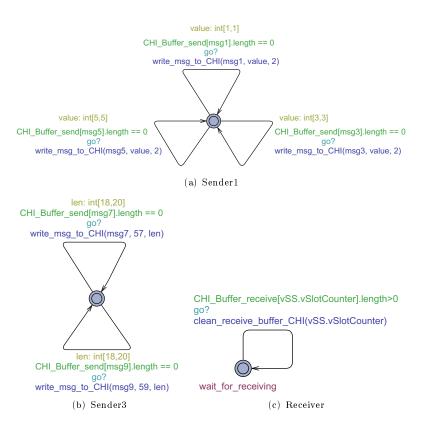

In the first step,  $H_1$  and  $B_1$  are composed, so that event  $!put_1$  becomes an uncontrollable local event and can be hidden. Thus,  $H_1$  and  $B_1$  are replaced by  $HB_1 = (H_1 || B_1) \setminus \{!put_1\}$  shown in Fig. 4, where for graphical simplicity the two blocking states from Fig. 1 are replaced by the state  $\bot$ . Clearly, such blocking states must be avoided, and since the silent uncontrollable transition  $5 \stackrel{\tau_u}{\to} \bot$  cannot be disabled by the supervisor or by any plant, state 5 must also be avoided. States 5 and  $\bot$  are *certainly unsupervisable states* and are crossed out in Fig. 4. Automaton  $HB_1$  is replaced by the synthesis equivalent abstraction  $HB_1$  with 5 states, which is obtained by deleting states 5 and  $\bot$ . The same abstraction is applied to the other buffers and handlers.

After composition of  $W_1$ , *Produce*, and *Lock*, events !sus, !res, !lock, and unlock are local and can be hidden. Fig. 4 shows the result  $W = (W_1 \parallel Produce \parallel Lock) \setminus_!$ {!sus, !res, !lock, unlock}. Clearly, states  $\perp_1$  and  $\perp_2$  are blocking states. Moreover, the only way for state 1 to reach an accepting state is via the transition  $1 \xrightarrow{|output_1|} 5$ . However,  $1 \xrightarrow{\tau_u} 2 \xrightarrow{|output_1|} \perp_1$ , and since neither the supervisor nor any other plant can disable  $\tau_u$ , a supervisor that enables event !output\_1 in state 1, inevitably permits the blocking state  $\perp_1$ . State 1 is a certainly unsupervisable state, and similar arguments hold for states 2, 3, 5, 6, and 7. Deleting these states from W results in the synthesis equivalent automaton  $\tilde{W}$ . Next,  $M_1$  and  $\tilde{W}$  are composed, which results in !output\_1 becoming a local event. The composed automaton, MW, has 28 states. Applying certain unsupervisability results in  $\tilde{MW}$  with 20 states. Replacing  $W_1$ , Produce, and Lock by  $\tilde{MW}$  gives the final abstracted system  $\tilde{\mathscr{G}} = \tilde{MW} \parallel M_2 \parallel H\tilde{B}_1 \parallel H\tilde{B}_2 \parallel H\tilde{B}_3 \parallel H\tilde{B}_4$ .

Finally, the components of  $\tilde{\mathscr{G}}$  are composed to calculate a supervisor. This requires the exploration of the synchronous composition  $\tilde{\mathscr{G}}$  with 48400 states, in contrast to the state space of the original system  $\mathscr{G}$  with  $1.3 \times 10^6$  states. The final supervisors calculated from  $\mathscr{G}$  and  $\tilde{\mathscr{G}}$  are identical and have 4374 states.

### 4 Certain Unsupervisability

#### 4.1 Certainly Unsupervisable States and Transitions

The above example shows that some states of an automaton G must be avoided by synthesis in every possible context. That is, no matter what other automata are later composed with G, it is clear that these states are unsafe. Blocking states are examples of such states, but there are more states with this property.

**Definition 10.** Let  $G = \langle \Sigma, Q, \rightarrow, Q^{\circ}, Q^{\omega} \rangle$  be an automaton. The *certainly unsupervisable state set* of *G* is

$$\hat{U}(G) = \{ x \in Q \mid \text{for every automaton } T = \langle \Sigma, Q_T, \to_T, Q_T^\circ, Q_T^\omega \rangle \text{ and every } (9) \\ \text{state } x^T \in Q_T \text{ it holds that } (x, x^T) \notin \hat{\Theta}_{G \parallel T} \}.$$

A state *x* of *G* is certainly unsupervisable, if there exists no other automaton *T* such that the state *x* is present in the least restrictive synthesis result  $\hat{\Theta}_{G||T}$ . If a state is certainly unsupervisable, it is known that this state will be removed by any synthesis. If such states are encountered in an automaton during compositional synthesis, they can be removed before composing this automaton further.

**Example 3.** Consider again automaton  $HB_1$  in Fig. 4. Clearly, the blocking state  $\perp$  is certainly unsupervisable. In addition, state 5 is also certainly unsupervisable, because of the local uncontrollable transition  $5 \xrightarrow{\tau_u} \perp$ . As this transition is silent, no other component disables it, and as it is uncontrollable, the supervisor cannot disable it. Therefore, if the automaton ever enters state 5, blocking is unavoidable. It holds that  $\hat{U}(HB_1) = \{5, \bot\}$ .

In addition to states, it is worth considering transitions as certainly unsupervisable. If an uncontrollable event v can take a state x to a certainly unsupervisable state, then all v-transitions from x are certainly unsupervisable. Such transitions can be removed because it is clear that no supervisor will allow state x to be entered while v is possible in the plant.

**Definition 11.** Let  $G = \langle \Sigma, Q, \to, Q^{\circ}, Q^{\omega} \rangle$  be an automaton. A transition  $x \xrightarrow{\upsilon} y$  with  $\upsilon \in \Sigma_{u}$  is a *certainly unsupervisable transition* if  $x \xrightarrow{\tau_{u}^{*}\upsilon} \hat{U}(G)$ .

**Example 4.** Consider automaton *W* in Fig. 4. States  $\bot_1$ ,  $\bot_2$ , and  $\bot_3$  are blocking and therefore certainly unsupervisable. State 5 is also certainly unsupervisable, because every path from state 5 to an accepting state must take the transition 5  $\xrightarrow{|output_1|}$  9. However, this transition is certainly unsupervisable, as  $!output_1$  is uncontrollable and  $5 \xrightarrow{\tau_u} 6 \xrightarrow{|output_1|} \bot_2 \in \hat{U}(W)$ . The only way for a potential supervisor to avoid the blocking state  $\bot_2$  is to also avoid state 5. By similar arguments, it follows that  $\hat{U}(W) = \{1, 2, 3, 5, 6, 7, \bot_1, \bot_2, \bot_3\}$ .

If the certainly unsupervisable states and transitions are known, they can be used to simplify an automaton to form a synthesis equivalent *abstraction*.

**Definition 12.** Let  $G = \langle \Sigma, Q, \rightarrow, Q^{\circ}, Q^{\omega} \rangle$  be an automaton. The result of *unsupervisability removal* from *G* is the automaton

$$\operatorname{unsup}\mathscr{C}(G) = \langle \Sigma, Q, \to_{\operatorname{unsup}}, Q^{\circ} \setminus \hat{U}(G), Q^{\omega} \setminus \hat{U}(G) \rangle , \qquad (10)$$

where

$$\rightarrow_{\text{unsup}} = \{ (x, \sigma, y) \in \rightarrow \mid \sigma \in \Sigma_c \text{ and } x, y \notin \hat{U}(G) \} \cup$$

(11)

$$\{(x, v, y) \in \to | v \in \Sigma_{u}, x \notin \hat{U}(G), \text{ and } y \in \hat{U}(G)\} \cup$$

$$\tau^{*}v \qquad (12)$$

$$\{(x, v, y) \in \rightarrow | v \in \Sigma_{u}, x \notin \hat{U}(G), \text{ and } x \xrightarrow{\tau_{u} v} \hat{U}(G) \text{ does not hold } \}.$$

(13)

All controllable transitions to unsupervisable states are removed (11), as these transitions can always be disabled by the supervisor and therefore never appear in the final synthesis result. Uncontrollable transitions to certainly unsupervisable states, however, are retained (12), because they are needed to inform future synthesis step. If another component disables these events, they may disappear in synchronous composition with that component, otherwise the source state may have to be removed in synthesis. Uncontrollable transitions to other states are deleted if they are certainly unsupervisable (13).

**Example 5.** When applied to automaton W in Fig. 4, unsupervisability removal deletes all transitions linked to the crossed out states. While state  $\perp_3$  is also certainly unsupervisable, the shared uncontrollable !output\_1-transitions to this state are retained. They are needed in the following steps of compositional synthesis. If some other component disables !output\_1 while in state 10 or 11, then these states may be retained, otherwise they will be removed at a later stage.

The following theorem confirms that unsupervisability removal results in a synthesis equivalent automaton. Therefore, the abstraction can be used to replace an automaton during compositional synthesis without affecting the final synthesis result.

#### **Theorem 3.** Let *G* be an automaton. Then $G \simeq_{\text{synth}} \text{unsup} \mathscr{C}(G)$ .

Unsupervisability removal by definition only removes transitions and no states. Yet, states may become unreachable as a result of transition removal, and unreachable states can always be removed. Furthermore, it is possible to combine all remaining unsupervisable states, which have no outgoing transitions, into a single state [16].

### 4.2 Iterative Characterisation

The following definition provides an alternative characterisation of the certainly unsupervisable states through an iteration. It forms the basis for an algorithm to compute the set of certainly unsupervisable states. **Definition 13.** Let  $G = \langle \Sigma, Q, \rightarrow, Q^{\circ}, Q^{\omega} \rangle$  be an automaton. Define the set U(G) inductively as follows.

$$U^0(G) = \emptyset ; \tag{14}$$

$U^{k+1}(G) = \{ x \in Q \mid \text{for all paths } x = x_0 \xrightarrow{\sigma_1} \cdots \xrightarrow{\sigma_n} x_n \in Q^{\omega} \text{ there exists } i = 0, \dots, n \quad (15)$

such that

$$x_i \xrightarrow{\cdot_{\mathbf{u}}} U^k(G)$$

or  $i > 0$  and  $\sigma_i \in \Sigma_{\mathbf{u}}$  and  $x_{i-1} \xrightarrow{\cdot_{\mathbf{u}} \circ \iota_{-\mathbf{u}}} U^k(G)$  ;

$U(G) = \bigcup_{k \ge 0} U^k(G)$  . (16)

The set  $U^k(G)$  contains unsupervisable states of *level k*. There are no unsupervisable states of level 0, and the unsupervisable states of level 1 are the blocking states, i.e., those states from where it is not possible to ever reach an accepting state. Unsupervisable states at a higher level are states from where every path to an accepting state is known to pass through an unsupervisable state or an unsupervisable transition of a lower level.

**Example 6.** Consider automaton *W* in Fig. 4. It holds that  $U^0(W) = \emptyset$ , and  $U^1(W) = \{\perp_1, \perp_2, \perp_3\}$  contains the three blocking states. Next, it can be seen that  $1 \in U^2(W)$ , because every path from 1 to an accepting state includes the transition  $1 \xrightarrow{|\text{output}_1|} 5$  with  $|\text{output}_1 \in \Sigma_u$  and  $1 \xrightarrow{\pi_u} 2 \xrightarrow{|\text{output}_1|} \perp_1 \in U^1(W)$ . Likewise, it holds that 2,3,5,6,7  $\in U^2(W)$ . No further states are contained in  $U^2(W)$  or in  $U^k(W)$  for k > 2, so that  $U(W) = U^2(W) = \{1, 2, 3, 5, 6, 7, \perp_1, \perp_2, \perp_3\} = \hat{U}(W)$ .

The following Theorem 4 confirms that the iteration  $U^k(G)$  reaches the set of certainly unsupervisable states.

**Theorem 4.** Let  $G = \langle \Sigma, Q, \rightarrow, Q^{\circ}, Q^{\omega} \rangle$  be an automaton. Then  $U(G) = \hat{U}(G)$ .

#### 4.3 Algorithm

To determine whether some state x is contained in the set  $U^{k+1}(G)$  of unsupervisable states of a new level, the definition (15) considers all paths from state x to an accepting state. Such a condition is difficult to implement directly. It is more feasible to search backwards from the accepting states using the following secondary iteration.

**Definition 14.** Let  $G = \langle \Sigma, Q, \rightarrow, Q^{\circ}, Q^{\omega} \rangle$  be an automaton. Define the sets of *supervisable states*  $S^k(G)$  for  $k \ge 1$  inductively as follows.

$$S_0^{k+1}(G) = \{ x \in Q^{\omega} \mid x \stackrel{\tau_u^*}{\to} U^k(G) \text{ does not hold } \};$$

(17)

$$S_{j+1}^{k+1}(G) = \{ x \in Q \mid x \xrightarrow{\sigma} S_j^{k+1}(G), \text{ and } x \xrightarrow{\tau_u^*} U^k(G) \text{ does not hold, and if } (18)$$

$$S^{k+1}(G) = \bigcup_{j \ge 0} S^{k+1}_j(G) .$$

(19)

Given the set  $U^k(G)$  of unsupervisable states at level k, the iteration  $S_j^{k+1}(G)$  computes a set of supervisable states, i.e., states from where a supervisor can reach an accepting state while avoiding the unsupervisable states in  $U^k(G)$ . The process starts as a backwards search from those accepting states from where it is not possible to reach a known unsupervisable state using only  $\tau_u$ -transitions (17). Then transitions leading to the states already found are explored backwards (18). However, source states x that can reach a known unsupervisable state using only  $\tau_u$ -transitions ( $x \xrightarrow{\tau_u^*} U^k(G)$ ), and known unsupervisable transitions ( $x \xrightarrow{\tau_u^*} \sigma \tau_u^* \cup U^k(G)$ ) are excluded.

**Example 7.** As shown in Example 6, the first iteration for unsupervisable states of automaton *W* in Fig. 4 gives the blocking states,  $U^1(W) = \{\perp_1, \perp_2, \perp_3\}$ . Then the first set of supervisable states for the next level contains the two accepting states,  $S_0^2(W) = \{8,9\}$  according to (17). Then  $4 \xrightarrow{!output_1} 8 \in S_0^2(W)$  and  $8 \xrightarrow{\tau_u} 9 \in S_0^2(W)$  and  $10 \xrightarrow{\tau_u} 9 \in S_0^2(W)$ , and it does not hold that  $4 \xrightarrow{\tau_u^*} U^1(W)$  or  $4 \xrightarrow{\tau_u^*!output_1\tau_u^*} U^1(W)$  or  $8 \xrightarrow{\tau_u^*} U^1(W)$  or  $10 \xrightarrow{\tau_u^*} U^1(W)$ . Therefore,  $S_1^2(W) = \{4,8,10\}$  according to (18). Note that  $5 \notin S_1^2(W)$  because despite the transition  $5 \xrightarrow{!output_1} 9$  it holds that  $5 \xrightarrow{\tau_u} 6 \xrightarrow{!output_1} \perp_2 \in U^1(W)$ . The next iteration gives  $S_2^2(W) = \{0,4,8,9,10,11\} = Q \setminus U^2(W)$ .

The following theorem confirms that the iteration  $S_j^{k+1}(G)$  converges against the complement of the next level of unsupervisable states,  $U^{k+1}(G)$ .

**Theorem 5.** Let  $G = \langle \Sigma, Q, \rightarrow, Q^{\circ}, Q^{\omega} \rangle$  be an automaton. For all  $k \ge 1$  it holds that  $S^k(G) = Q \setminus U^k(G)$ .

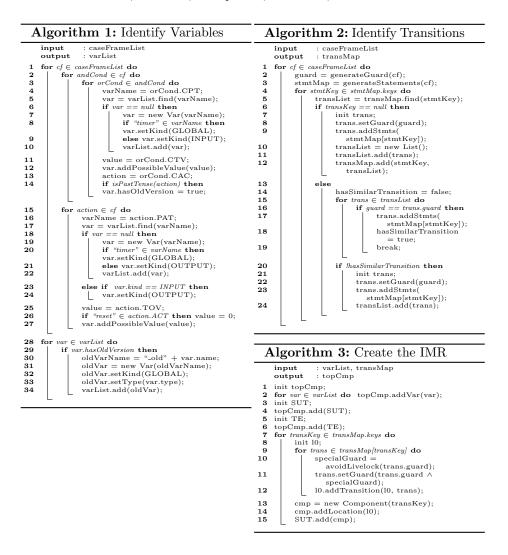

Algorithm 1 is an implementation of the iterations in Def. 13 and 14 to compute the set of certainly unsupervisable states for a given automaton G. First, the sets of certainly unsupervisable states U and certainly unsupervisable transitions UT are initialised in lines 2 and 3. Then the loop in lines 4–28 performs the iterations for  $U^k(G)$ .

The first step is to compute the supervisable states  $S_0^{k+1}(G)$ , which are stored in *S*. In line 5, this variable is initialised to the set  $S_0^{k+1}(G)$  containing the accepting states that are not yet known to be unsupervisable. Then the loop in lines 7–15 uses a *stack* to perform a backwards search over the transition relation, avoiding known unsupervisable source states and known unsupervisable transitions. Upon termination, the variable *S* contains the set  $S^{k+1}(G)$  of supervisable state for the next level.

Then the loop in lines 17–27 updates the sets U and UT. For every state that was not added to S, it explores the predecessor states reachable by sequences of  $\tau_u$ -transitions, and adds any states found to U, if not yet included. By adding the  $\tau_u$ -predecessors to the set U immediately, the reachability tests in (17) and (18) can be replaced by the direct membership tests in line 10. Next, for any new unsupervisable state x, the loop in lines 21–25, searches for possible uncontrollable transitions followed by sequences of  $\tau_u$  and adds such combinations of source states and uncontrollable events to the set certainly unsupervisable transitions UT.

The algorithm terminates if no new unsupervisable states are found during execution of the loop in lines 17–27, in which case the flag *done* retains its true value. At this point, the set U contains all certainly unsupervisable states.

Algorithm 1 Calculate U(G)

```

1: input G = \langle \Sigma, Q, \rightarrow, Q^{\circ}, Q^{\omega} \rangle

2: U \leftarrow \emptyset

3: UT \leftarrow \emptyset

4: repeat

S \leftarrow \{ x \in Q^{\omega} \mid x \notin U \}

5:

stack.init(S)

6:

7:

while stack not empty do

8:

x \leftarrow stack.pop()

for all w \xrightarrow{\sigma} x do

9:

if w \notin S and w \notin U and (w, \sigma) \notin UT then

10:

11:

S \leftarrow S \cup \{w\}

12:

stack.push(w)

13:

end if

14:

end for

15:

end while

16:

done \leftarrow true

for all x \xrightarrow{\tau_u^*} Q \setminus S do

17:

if x \notin U then

18:

U \leftarrow U \cup \{x\}

19:

done \leftarrow false

20:

for all \upsilon \in \Sigma_u \setminus \{\tau_u\} do

21:

for all w \xrightarrow{\tau_u^* \upsilon} x \operatorname{do}

22:

UT \leftarrow UT \cup \{(w, v)\}

23:

24:

end for

25:

end for

26:

end if

27:

end for

28: until done

29: return U

```

# 4.4 Complexity

This section gives an estimate for the time complexity of Algorithm 1. Each iteration of the main loop in lines 4–28 must add at least one state to U, which gives at most |Q| iterations. During each of these iterations, the loop in lines 7–15 visits each transition at most once, giving up to  $|\rightarrow|$  iterations, and the loop in lines 17–27 visits up to |Q| predecessors of each state, which gives another  $|Q|^2$  iterations. Assuming that the closure of  $\tau_u$ -transitions is calculated in advance, these iterations, again assuming that the closure of  $\tau_u$ -transitions is calculated in advance. However, the inner loop not executed more than once per state during the entire algorithm. The complexity to compute the  $\tau_u$ -closure in advance is  $O(|Q|^3)$  [18].

Summing up these computation costs, the worst-case time complexity of Algorithm 1 is found to be:

$$O(|Q| \cdot (|\rightarrow| + |Q|^2) + |Q| \cdot |Q|^2 + |Q|^3) = O(|\Sigma||Q|^3).$$

(20)

Thus, the set of certainly unsupervisable states can be computed in polynomial time. This is surprising given the nondeterministic nature of similar problems, which require *subset construction* [12]. For example, the *set of certain conflicts* [14], which is the equivalent of the set of certainly unsupervisable states in nonblocking verification, can only be computed in exponential time. In synthesis, the assumption of a supervisor with the capability of full observation of the plant makes it possible to distinguish states and avoid subset construction.

#### 4.5 Halfway Synthesis

This section introduces *halfway synthesis* [9], which has been used previously [9, 16] to remove unsupervisable states in compositional synthesis, and compares it with the set of certainly unsupervisable states. It is shown that in general more states can be removed by taking certain unsupervisability into account.

**Definition 15.** Let  $G = \langle \Sigma, Q, \rightarrow, Q^{\circ}, Q^{\omega} \rangle$ , and let  $\hat{\Theta}_{G,\tau_{u}}$  be the greatest fixpoint of the synthesis step operator according to Def. 8, but computed under the assumption that  $\Sigma_{u} = \{\tau_{u}\}$ . The *halfway synthesis result* for *G* is hsup $\mathscr{C}(G) = \langle \Sigma, Q, \rightarrow_{hsup}, Q^{\circ} \cap \hat{\Theta}_{G,\tau_{u}}, Q^{\omega} \cap \hat{\Theta}_{G,\tau_{u}} \rangle$ , where

$$\rightarrow_{\text{hsup}} = \{ (x, \sigma, y) \in \rightarrow \mid x, y \in \hat{\Theta}_{G, \tau_{\mu}} \} \cup$$

(21)

$$\{(x, \upsilon, y) \in \to | x \in \hat{\Theta}_{G, \tau_{u}}, \ \upsilon \in \Sigma_{u} \setminus \{\tau_{u}\}, \text{ and } y \notin \hat{\Theta}_{G, \tau_{u}}\}$$

(22)

The idea of halfway synthesis is to use standard synthesis, but treating only the silent uncontrollable event  $\tau_u$  as uncontrollable. All other events are assumed to be controllable, because other plant components may yet disable shared uncontrollable events, so it is not guaranteed that these events cause controllability problems [9]. After computing the synthesis fixpoint  $\hat{\Theta}_{G,\tau_u}$ , the abstraction is obtained by removing controllable transitions to states not contained in  $\hat{\Theta}_{G,\tau_u}$ , while uncontrollable transitions are retained for the same reasons as in Def. 12.

**Theorem 6.** Let *G* be an automaton. Then  $unsup \mathscr{C}(G) \subseteq hsup \mathscr{C}(G)$ .

**Example 8.** When applied to automaton  $H_1 || B_1$  in Fig. 4, halfway synthesis removes the crossed out states and produces the same result as unsupervisability removal. However, it only considers states  $\bot_1$ ,  $\bot_2$ , and  $\bot_3$  of W in Fig. 4 as unsupervisable, because the shared uncontrollable event !output\_1 is treated as a controllable event. This automaton is left unchanged by halfway synthesis.

Halfway synthesis only removes those unsupervisable states that can reach a blocking state via local uncontrollable  $\tau_u$ -transitions, but it does not take into account certainly unsupervisable transitions. Theorem 6 confirms that unsupervisability removal achieves all the simplification achieved by halfway synthesis, and Example 8 shows that there are cases where unsupervisability removal can do more. On the other hand, the complexity of halfway synthesis is the same as for standard synthesis,  $O(|\Sigma||Q|^3)$ , which is the same as found above for certain unsupervisability (20).

### 5 Conclusions

The set of *certainly unsupervisable states* of an automaton comprises all the states that must be avoided during synthesis of a controllable and nonblocking supervisor, in every possible context. In compositional synthesis, the removal of certainly unsupervisable states gives rise to a better abstraction than the previously used halfway synthesis, while maintaining the same cubic complexity.

The results of this paper are not intended to be used in isolation. In future work, the authors will integrate the removal of certainly unsupervisable states with their compositional synthesis framework [16]. It will be investigated in what order to apply unsupervisability removal and other abstraction methods, and how to group automata together for best performance.

Certainly unsupervisable states are also of crucial importance to determine whether two states of an automaton can be treated as equivalent for synthesis purposes. The results of this paper can be extended to develop abstraction methods that identify and merge equivalent states in compositional synthesis.

# References

- de Alfaro, L., Henzinger, T.A.: Interface automata. In: Proc. 9th ACM SIGSOFT Int. Symp. on Foundations of Software Engineering 2001. pp. 109–120. Vienna, Austria (2001)

- Asarin, E., Maler, O., Pnueli, A.: Symbolic controller synthesis for discrete and timed systems. In: Hybrid Systems II, LNCS, vol. 999, pp. 1–20. Springer (1995)

- Aziz, A., Singhal, V., Swamy, G.M., Brayton, R.K.: Minimizing interacting finite state machines: A compositional approach to language containment. In: Proc. Int. Conf. Computer Design (1994)

- 4. Baier, C., Katoen, J.P.: Principles of Model Checking. MIT Press (2008)

- Baier, C., Klein, J., Klüppelholz, S.: A compositional framework for controller synthesis. In: Katoen, J.P., König, B. (eds.) Proc. 22nd Int. Conf. Concurrency Theory, CONCUR 2011. LNCS, vol. 6901, pp. 512–527. Springer, Aachen, Germany (Sep 2011)

- 6. Fabian, M.: On Object Oriented Nondeterministic Supervisory Control. Ph.D. thesis, Chalmers University of Technology, Göteborg, Sweden (1995), https://publications. lib.chalmers.se/cpl/record/index.xsql?publd=1126

- Filiot, E., Jin, N., Raskin, J.F.: Compositional algorithms for LTL synthesis. In: Chin, W.N. (ed.) Proc. 8th Int. Symp. Automated Technology for Verification and Analysis, ATVA 2010. LNCS, vol. 6252, pp. 112–127. Springer, Singapore, Singapore (Sep 2010)

- Flordal, H., Malik, R.: Compositional verification in supervisory control. SIAM J. Control and Optimization 48(3), 1914–1938 (2009)

- Flordal, H., Malik, R., Fabian, M., Åkesson, K.: Compositional synthesis of maximally permissive supervisors using supervision equivalence. Discrete Event Dyn. Syst. 17(4), 475–504 (2007)

- Gohari, P., Wonham, W.M.: On the complexity of supervisory control design in the RW framework. IEEE Trans. Syst., Man, Cybern. (Aug 2000)

- 11. Hoare, C.A.R.: Communicating Sequential Processes. Prentice-Hall (1985)

- 12. Hopcroft, J.E., Motwani, R., Ullman, J.D.: Introduction to Automata Theory, Languages, and Computation. Addison-Wesley (2001)

- 13. Lin, F., Wonham, W.M.: Decentralized control and coordination of discrete-event systems with partial observation. IEEE Trans. Autom. Control 35(12), 1330–1337 (Dec 1990)

- 14. Malik, R.: The language of certain conflicts of a nondeterministic process. Working Paper 05/2010, Dept. of Computer Science, University of Waikato, Hamilton, New Zealand (2010)

- Malik, R., Streader, D., Reeves, S.: Conflicts and fair testing. Int. J. Found. Comput. Sci. 17(4), 797–813 (2006)

- 16. Mohajerani, S., Malik, R., Fabian, M.: A framework for compositional synthesis of modular nonblocking supervisors. IEEE Trans. Autom. Control (Jan 2014), to appear

- 17. Mooij, A.J., Stahl, C., Voorhoeve, M.: Relating fair testing and accordance for service replaceability. J. Logic and Algebraic Programming 79(3–5), 233–244 (Apr–Jul 2010)

- Nuutila, E.: Efficient Transitive Closure Compution in Large Digraphs, Acta Polytechnica Scandinavica, Mathematics and Computing in Engineering Series, vol. 74. Finnish Academy of Technology, Helsinki, Finland (1995)

- Pnueli, A., Rosner, R.: On the synthesis of a reactive module. In: Proc. 16th ACM Symp. Principles of Programming Languages. pp. 179–190 (1989)

- Wonham, W.M.: On the control of discrete-event systems. In: Nijmeijer, H., Schumacher, J.M. (eds.) Three Decades of Mathematical System Theory. LNCIS, vol. 135, pp. 542–562. Springer (1989)

# Wind Turbine System : An Industrial Case Study in Formal Modeling and Verification

Jagadish Suryadevara<sup>1</sup>, Gaetana Sapienza<sup>2</sup>, Cristina Seceleanu<sup>1</sup>, Tiberiu Seceleanu<sup>2</sup>, Stein-Erik Ellevseth<sup>2</sup>, and Paul Pettersson<sup>1</sup>

<sup>1</sup> Mälardalen Real-Time Research Centre, Mälardalen University, Västerås, Sweden. {jagadish.suryadevara, cristina.seceleanu, paul.pettersson}@mdh.se <sup>2</sup> ABB Corporate Research. {gaetana.sapienza, tiberiu.seceleanu}@se.abb.com,

stein-erik.ellevseth@no.abb.com

**Abstract.** In the development of embedded systems, the formal analysis of system artifacts, such as structural and behavioral models, helps the system engineers to understand the overall functional and timing behavior of the system. In this case study paper, we present our experience in applying formal *verification and validation* (V&V) techniques, we had earlier proposed, for an industrial *wind turbine system* (WTS). We demonstrate the complementary benefits of formal verification and *testing*. We also discuss some modeling *trade-offs* and challenges we have identified with the case-study, which are worth being emphasized. One issue is related, for instance, to the *expressiveness* of the system artifacts, in view of the known limitations of rigorous verification, e.g. *model-checking*, of industrial systems.

Keywords: Industrial Case-Study, Wind Turbine System, MARTE/CCSL, EAST-ADL, Verification, Model Checking, UPPAAL

# 1 Introduction

The increasing complexity and criticality of real-time embedded systems (RTES), in domains such as industrial automation, automotive and avionics, stresses the need for applying systematic design phases, combined with rigorous *verification and validation* (V&V) techniques, during system development [3]. A well-defined design process with necessary tool support leads to ensuring system *predictability*, w.r.t intended functional and timing behavior. Nevertheless, meeting such a clear objective has several challenges. One of pre-requisites is well-defined system artifacts representing system *structure* as well as *behavior* with *reactive, continuous, discrete,* and *real-time* features, or a combination thereof, at suitable *levels-of-abstraction*. For complex industrial systems, the above design by-products, while necessary, may lead to additional issues such as ensuring *traceability, analyzability* as well as *reusability* of the system artifacts. In this context, model-based development approaches, which enable continuous V&V throughout the development process, have become a feasible solution to tackle some of the challenges. However, formal verification techniques such as *model checking*, while useful for the exhaustive analysis of system behavior, are challenging to apply for complex system models. A related issue is choosing a suitable level of *granularity* and *expressiveness* for system artifacts, given the well-known limitations of model-checking, such as the *state-space explosion* problem. In this paper, we address some of these challenges in the context of applying modeling and formal verification techniques using a *wind turbine system* case-study, a complex industrial RTES.

The Unified Modeling Language (UML) provides a modeling profile called MARTE (Modeling and Analysis of Real-Time and Embedded systems) [7] to support the *performance* and *schedulability* analysis of system models. MARTE also includes CCSL – a time model and a *clock constraint specification language* [1] for specifying logical and chronometric constraints for system models. On the other hand, EAST-ADL [2], an emerging standard for automotive systems, provides an integrated model-based development for RTES, through well-defined phases, as well as support for *traceability*. Recently, EAST-ADL has been integrated with *model-checking* support for component-based designs, e.g. the ViTAL tool [4] based on the timed automata technology for verification [5,11,10].

In this paper, we target the verification of functionality and timing behavior of a *wind turbine* system developed in the context of the iFEST (industrial Framework for Embedded Systems Tools), an ARTEMISIA project. In Section 2.2, we overview a simplified version of the *wind turbine system* (WTS), and describe its functionality and timing behavior. Rest of the paper is organized as follows: In Section 3, we briefly recall CCSL and timed automata. In Section 4, we describe a modeling methodology for the WTS to enable verification using *model checking*. The analysis results of simulating, as well as model checking the WTS model are presented in Section 5. In Section 6, we discuss our experience with the case study with respect to the challenges and limitations in applying formal techniques to complex industrial systems. We conclude the paper in Section 7.

# 2 Windturbine System (WTS) : An overview

Wind energy sources are fast-growing and in line with the technological advancement. Modern wind turbine systems require sophisticated and effective control functionalities in order to fulfill *performance*, *safety*, and *maintainability* requirements. The main purpose of a wind turbine system is to convert the rotational mechanical energy of the rotor blades (i.e. mechanical components of a wind turbine) caused by the wind into electrical energy to be redistributed via a power grid. Given the system's complexity, the iFEST (industrial Framework for Embedded Systems Tools) project<sup>3</sup> aims at providing a model-based approach for system development, to ensure the system *predictability* w.r.t the specified functional and timing behavior.

### 2.1 Development Process and Environment

In the iFEST project, we have carried out the system development by adopting the Vmodel based software development approach, as follows:

<sup>&</sup>lt;sup>3</sup> http://www.artemis-ifest.eu/

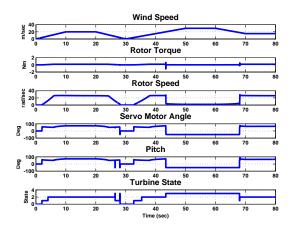

During *Requirement and Analysis* phase, we have documented the WTS requirements, both functional and extra-functional including timing behavior. For the *Design* phase, we have combined component- and model-based approaches, keeping in view the overall system *analyzability* and *reusability* requirements. During the *Implementation* phase, we have applied automatic code generation technologies.Subsequently, the implemented system, a combined FPGA and CPU solution, has been deployed on a heterogenous hardware platform (XilinX ZynQ 7000 product family). For the *Verification and Validation* (V&V), we have used model-based techniques as follows: (i) simulation of the WTS functionality using Simulink and related toolboxes, and (ii) automatic model-based test-case generation with MaTeLo tool. However, the above techniques are not sufficient to ensure system *predictability* w.r.t to all possible system executions, hence formal verification is desirable to complement the current analysis methods. To address the above open issue, in this paper, we present a verification technique towards enhanced system validation. And, our contributions are as below:

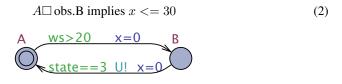

- As enhanced system validation, we apply verification technique to establish system properties, (partially) based on simulation results of Simulink-based system models.

- We are able to verify safety requirements that involve timing behavior (e.g. "the wind turbine moves to Park mode, within 30s of detecting that the wind speed has crossed the upper limit of 20m/sec").

#### 2.2 The Wind Turbine System Model

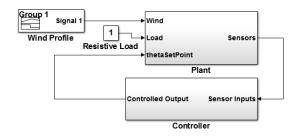

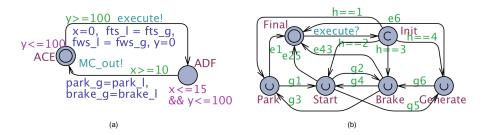

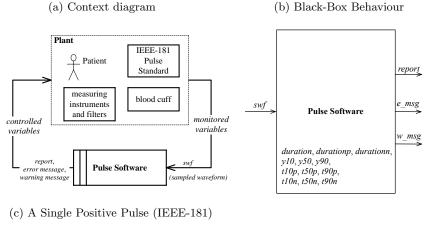

The wind turbine system is modeled as a *closed-loop* control system, as shown in Figure 1. The key components are the *Plant* and the *Controller* subsystems. The *Controller* dynamically regulates the rotor blades of the *wind turbine* w.r.t the specified wind profile, to maximize the generation of electrical energy and also to avoid damage to the plant in case of turbulent wind scenarios. It automatically changes the *Controller Output* signal to regulate the plant, based on the wind and the plant's actual conditions, which are received by the *Controller* via the *Sensor Input* signals. The *Wind Profile* and the *Resistive Load* are used to simulate and test the behavior of the plant and the controller, under specific wind and resistive load conditions. Further details of the plant and controller subsystems are described below.

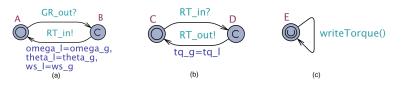

**2.2.1 Plant model.** As shown in Figure 2 (in Section 4), it consists of three main components; *Servo, Rotor*, and *Generator*. The pitch of the turbine, determined by the *Controller* (described below), is actuated by the *Servo*. The *Rotor* produces the required *torque* to maximize the angular speed of the *Generator* (which produces the final voltage), based on the pitch value as well as the current wind speed (we assume a fixed *resistive load*). The *Rotor* optimizes the produced torque value based on the current angular speed of the *Generator*.

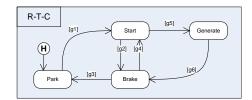

**2.2.2 Controller model.** As shown in Figure 3 (in Section 4), it consists of four main components: the *Filter*, the *Main Controller*, the *Pitch Controller*, and the *Park*

Fig. 1. Wind Turbine System Model

and Brake Controller. The Filter Subsystem is responsible for transducing, filtering and scaling the wind signal and plant signal (for instance the rotational speed of the turbine), which are used by the Main Controller and the Pitch Controller. Based on the inputs received through the Filter, the Main Controller directs the overall control. It oversees the performance and operations of the turbine in order to maximize the energy production and prevent any damage to the plant. Based on the wind and plant state, the controller determines the operational mode (i.e. park, start-up, generating, or brake) of the turbine. The Pitch Control calculates the proper pitch i.e. angle to steer the rotor blades when the turbine starts up or generates power. The Pitch and Brake controller determines if the turbine needs to brake or park, to ensure the safety of the wind turbine, for instance, during wind turbulances.

## **3** Preliminaries

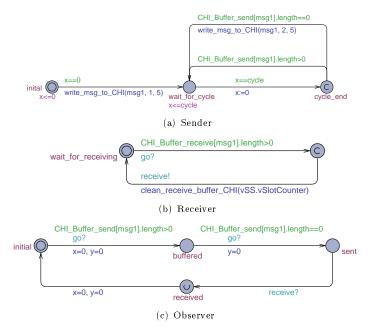

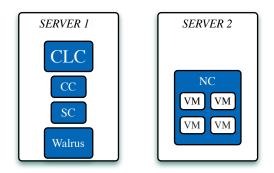

In this section, we present an overview of the preliminaries needed for modeling of the wind turbine system. We have used EAST-ADL modeling framework for structural modeling of the WTS. The timed causality behavior of the system is specified using CCSL. To provide the verification using the UPPAAL, a model checking tool, we have developed the timed automata based semantic models of the system, based on the corresponding EAST-ADL models and the CCSL specifications.

## 3.1 EAST-ADL

The modeling process in EAST-ADL framework, developed in the context of the EAST-EEA project, is structured into different abstraction levels such as *feature level*, *analysis level*, *design level* etc. At both analysis and design levels, the system is described by a *FunctionalArchitecture* that consists of a number of inter-connected *FunctionPrototypes* (instantiation of *FunctionType* components). FunctionProtoype components are either *event-* or *time-*triggered. The execution semantics of the EAST-ADL components is as follows; components interact through single buffer, *rewritable*, *non-consumable* ports, and execute in *read-execute-write* phases in *run-to-completion* fashion. The detailed timing behavior as well as timing constraints for an EAST-ADL model can be specified using TADL2, the Timing Augmented Description Language (ver 2), currently being integrated with EAST-ADL framework [8]. In related works, we have proposed verification techniques for TADL2-based EAST-ADL models [5,11,10].

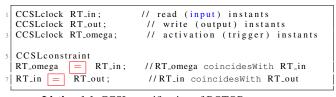

#### 3.2 CCSL

CCSL is used to specify the constraints imposed on the logical *clocks* (activation conditions) of a model. A CCSL clock is defined as a sequence of *instants* (event occurrences). CCSL constraints are of three kinds: (i) *Synchronous* constraints rely on the notion of *coincidence*. For example, the constraint "a coincidesWith b", denoted by a  $\equiv$  b, specifies that each instant of a coincides with the corresponding instant of b. Another example of a synchronous constraint is "a isPeriodicOn b period n", which specifies the subclock a whose 'ticks' correspond to every  $n^{th}$  'tick' of b. (ii) *Asynchronous* constraints are based on instant *precedence*; the constraint "a isFasterThan b" (denoted by a  $\leq$  b) specifies that clock a is (non-strictly) faster than clock b. (iii) *Mixed* constraints combine *coincidence* and *precedence*; the constraint "c = a delayedFor n on b" specifies that c 'ticks' synchronously with the  $n^{th}$  'tick' of b following a 'tick'.

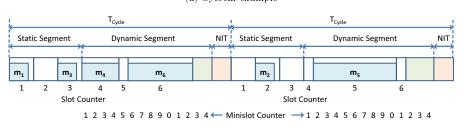

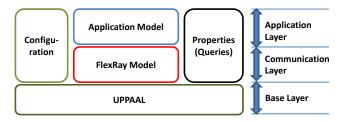

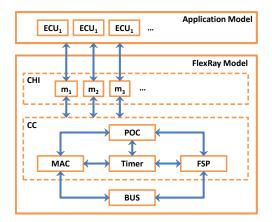

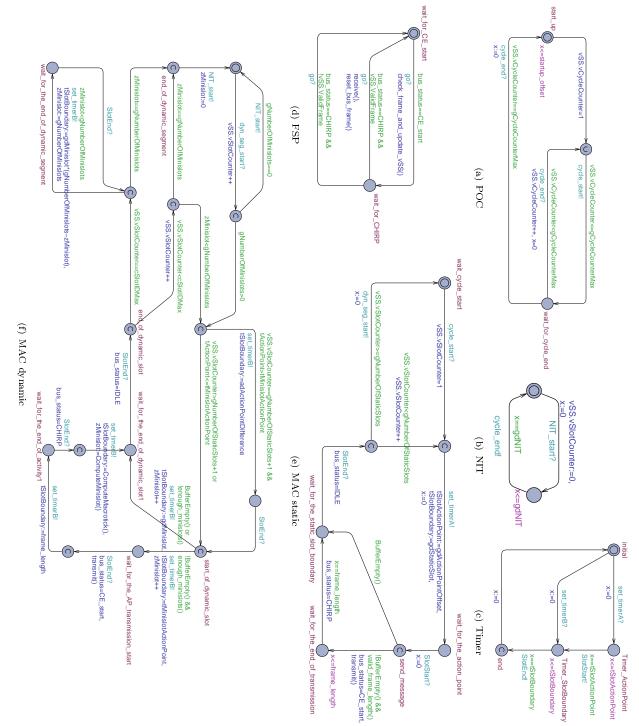

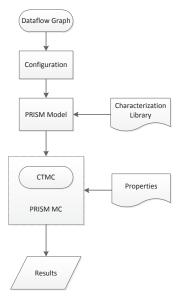

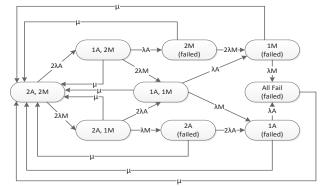

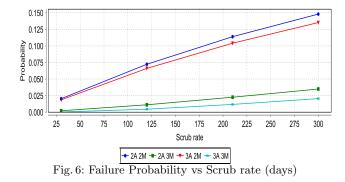

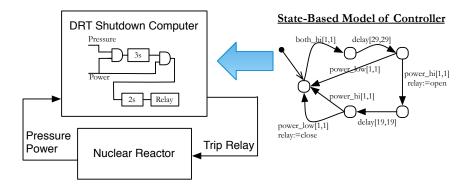

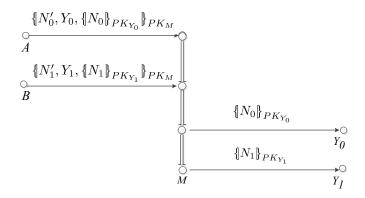

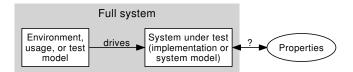

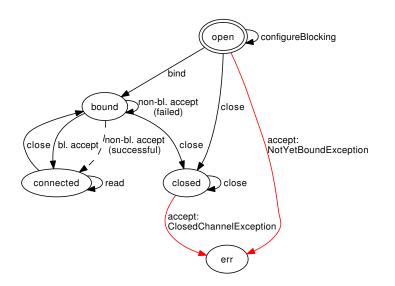

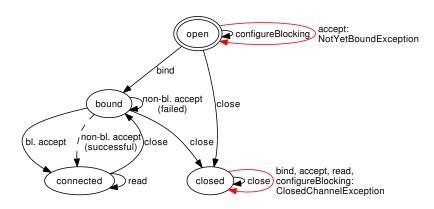

### 3.3 Timed Automata